Read/write time slot timing diagram figure 12, Read time slots – Rainbow Electronics DS1822-PAR User Manual

Page 14

DS1822-PAR

14 of 19

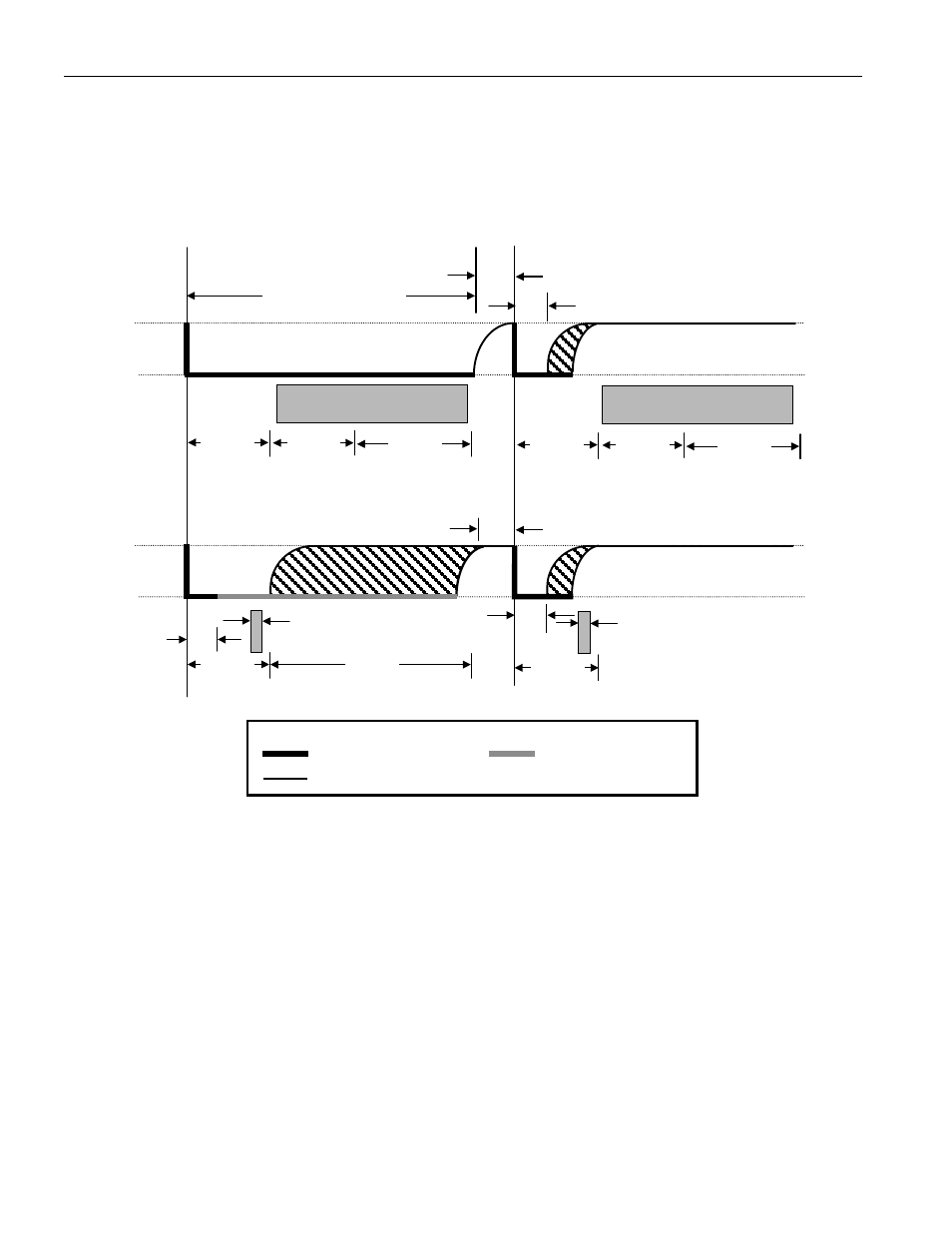

The DS1822-PAR samples the 1-wire bus during a window that lasts from 15

µ

s to 60

µ

s after the master

initiates the write time slot. If the bus is high during the sampling window, a 1 is written to the DS1822-

PAR. If the line is low, a 0 is written to the DS1822-PAR.

READ/WRITE TIME SLOT TIMING DIAGRAM Figure 12

READ TIME SLOTS

The DS1822-PAR can only transmit data to the master when the master issues read time slots. Therefore,

the master must generate read time slots immediately after issuing a Read Scratchpad [BEh] command, so

that the DS1822-PAR can provide the requested data. In addition, the master can generate read time slots

after issuing a Recall E

2

[B8h] command to find out the recall status as explained in the DS1822-PAR

FUNCTION COMMAND section.

All read time slots must be a minimum of 60

µ

s in duration with a minimum of a 1

µ

s recovery time

between slots. A read time slot is initiated by the master device pulling the 1-wire bus low for a

minimum of 1

µ

s and then releasing the bus (see Figure 12). After the master initiates the read time slot,

the DS1822-PAR will begin transmitting a 1 or 0 on bus. The DS1822-PAR transmits a 1 by leaving the

bus high and transmits a 0 by pulling the bus low. When transmitting a 0, the DS1822-PAR will release

the bus by the end of the time slot, and the bus will be pulled back to its high idle state by the pullup

LINE TYPE LEGEND

Bus master pulling low

DS1822-PAR pulling low

Resistor

pullup

45

µµµµ

s

15

µµµµ

s

V

PU

GND

1-WIRE BUS

60

µµµµ

s < T

X

“0” < 120

1

µµµµ

s < T

REC

<

∞

DS1822-PAR samples

MIN TYP MAX

15

µµµµ

s

30

µµµµ

s

> 1

µµµµ

s

MASTER WRITE “0” SLOT

MASTER WRITE “1” SLOT

DS1822-PAR samples

MIN TYP MAX

V

PU

GND

1-WIRE BUS

15

µµµµ

s

MASTER READ “0” SLOT

MASTER READ “1” SLOT

Master samples

Master samples

START

OF SLOT

START

OF SLOT

> 1

µµµµ

s

1

µµµµ

s < T

REC

<

∞

15

µµµµ

s

15

µµµµ

s

30

µµµµ

s

15

µµµµ

s

> 1

µµµµ

s