Voltage supervisor, Clock circuitry, I/o transceivers – Rainbow Electronics DS8314 User Manual

Page 9: Inactive mode, Activation sequence, Table 1. clock frequency selection, Table 2. card presence indication

Voltage Supervisor

The voltage supervisor monitors the V

DD

supply. A

220µs reset pulse (t

W

) is used internally to keep the

device inactive during power-on or power-off of the

V

DD

supply. See Figure 2.

The DS8313/DS8314 card interface remains inactive

regardless of the levels on the command lines until

duration t

W

after V

DD

has reached a level higher than

V

TH2

+ V

HYS2

. When V

DD

falls below V

TH2

, the

DS8313/DS8314 execute a card deactivation sequence

if their card interface is active.

Clock Circuitry

The card clock signal (CLK) is derived from a clock sig-

nal input to XTAL1 or from a crystal operating at up to

20MHz connected between XTAL1 and XTAL2. The

output clock frequency of CLK is selectable through

inputs CLKDIV1 and CLKDIV2. The CLK signal frequen-

cy can be f

XTAL

, f

XTAL

/2, f

XTAL

/4, or f

XTAL

/8. See Table

1 for the frequency generated on the CLK signal given

the inputs to CLKDIV1 and CLKDIV2.

Note that CLKDIV1 and CLKDIV2 must not be changed

simultaneously; a delay of 10ns minimum between

changes is needed. The minimum duration of any state

of CLK is eight periods of XTAL1.

The frequency change is synchronous: during a transition

of the clock divider, no pulse is shorter than 45% of the

smallest period, and the first and last clock pulses about

the instant of change have the correct width. When

changing the frequency dynamically, the change is effec-

tive for only eight periods of XTAL1 after the command.

The f

XTAL

duty factor depends on the input signal on

XTAL1. To reach a 45% to 55% duty factor on CLK,

XTAL1 should have a 48% to 52% duty factor with tran-

sition times less than 5% of the period.

With a crystal, the duty factor on CLK can be 45% to

55% depending on the circuit layout and on the crystal

characteristics and frequency. In other cases, the duty

factor on CLK is guaranteed between 45% and 55% of

the clock period.

I/O Transceivers

I/O and I/OIN are pulled high with an 11k

Ω resistor (I/O

to V

CC

and I/OIN to V

DD

) in the inactive state. The first

side of the transceiver to receive a falling edge

becomes the master. When a falling edge is detected

(and the master is decided), the detection of falling

edges on the line of the other side is disabled; that side

then becomes a slave. After a time delay t

D(EDGE)

, an n

transistor on the slave side is turned on, thus transmit-

ting the logic 0 present on the master side.

When the master side asserts a logic 1, a p transistor

on the slave side is activated during the time delay t

PU

and then both sides return to their inactive (pulled up)

states. This active pullup provides fast low-to-high tran-

sitions. After the duration of t

PU

, the output voltage

depends only on the internal pullup resistor and the

load current. Current to and from the card I/O lines is

limited internally to 15mA. The maximum frequency on

these lines is 1MHz.

Inactive Mode

The DS8313/DS8314 power up with the card interface

in the inactive mode. Minimal circuitry is active while

waiting for the host to initiate a smart card session.

• All card contacts are inactive (approximately 200

Ω

to GND).

• The I/OIN pin in the high-impedance state (11k

Ω

pullup resistor to V

DD

).

• Voltage generators are stopped.

• XTAL oscillator is running (if included in the device).

• Voltage supervisor is active.

• The internal oscillator is running at its low frequency.

Activation Sequence

After power-on and the reset delay, the host microcon-

troller can monitor card presence with signals OFF and

CMDVCC, as shown in Table 2.

DS8313/DS8314

Smart Card Interface

_______________________________________________________________________________________

9

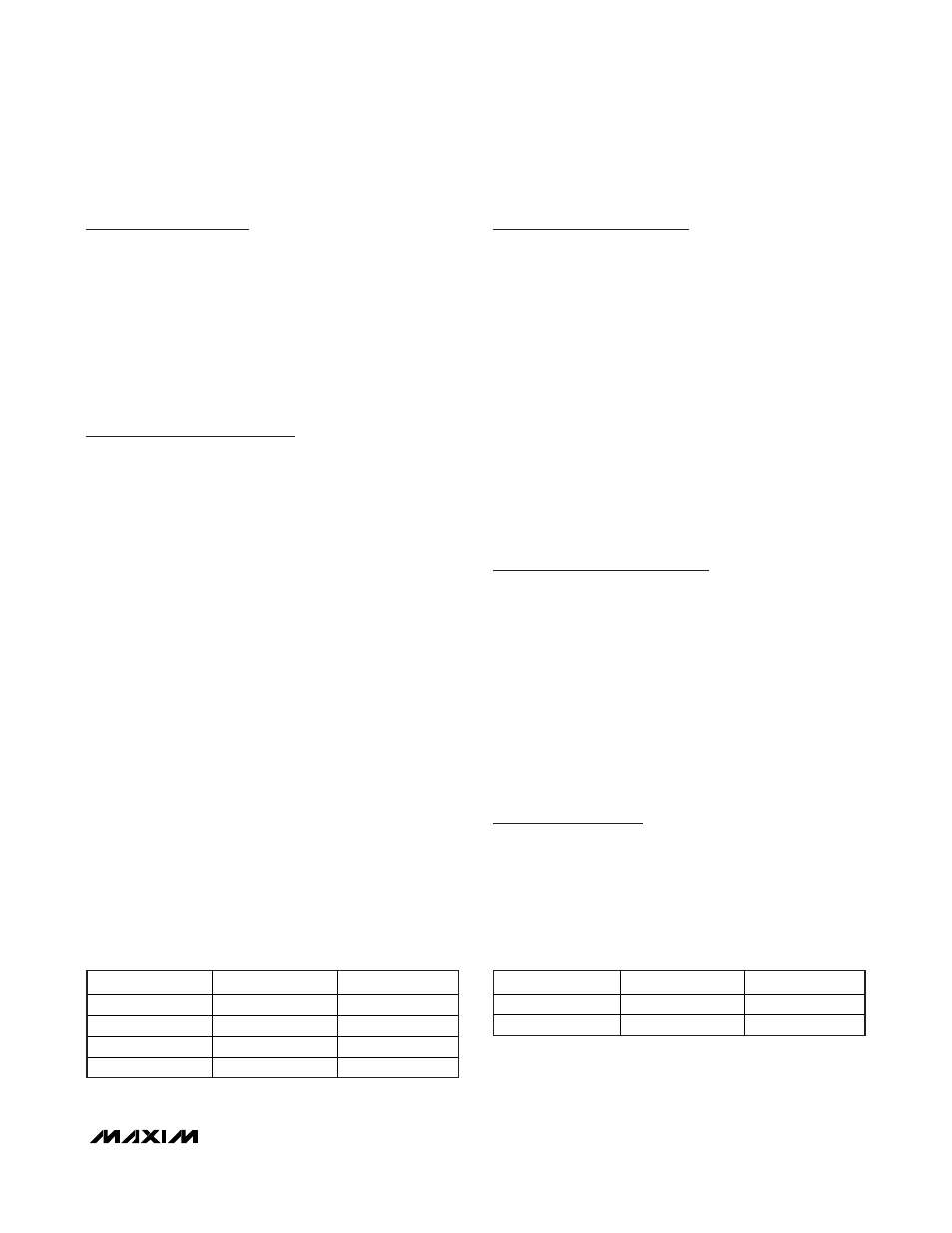

Table 1. Clock Frequency Selection

CLKDIV1

CLKDIV2

f

CLK

0 0

f

XTAL

/8

0 1

f

XTAL

/4

1 1

f

XTAL

/2

1 0

f

XTAL

Table 2. Card Presence Indication

OFF

CMDVCC

STATUS

High High

Card

present.

Low High

Card

not present.