Detailed pin description, Overview – Rainbow Electronics DS2404 User Manual

Page 2

DS2404

2 of 29

The DS2404 features can be used to create a stopwatch, alarm clock, time and date stamp, logbook, hour

meter, calendar, system power-cycle timer, expiration timer, and event scheduler.

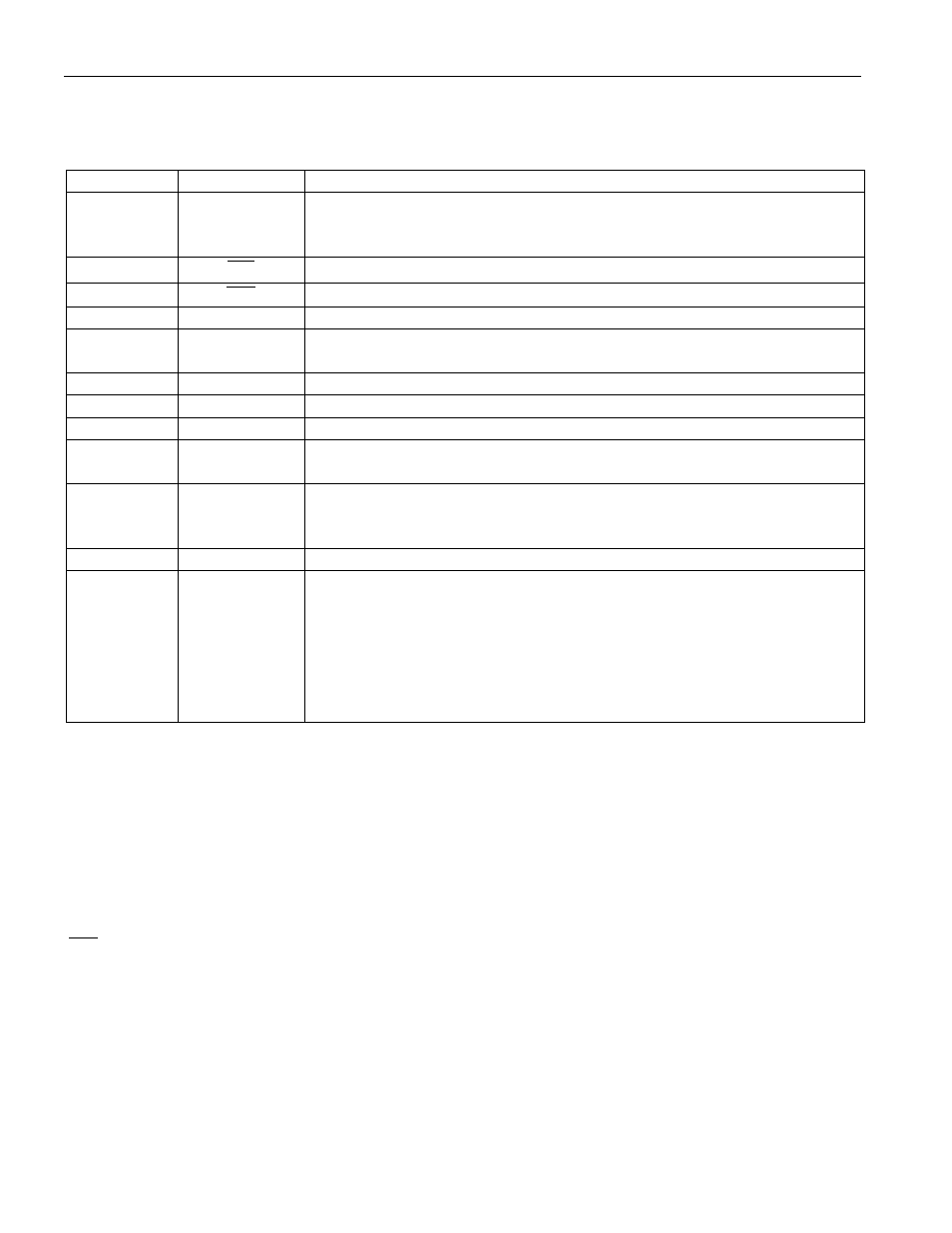

DETAILED PIN DESCRIPTION

PIN

SYMBOL

DESCRIPTION

1,16

V

CC

Power input pins for V

CC

operate mode. 2.8V to 5.5V operation. Either

one can be used for V

CC.

Only one is required for normal operation. (See

V

BATO

pin description and “Power Control” section).

2

IRQ

Interrupt output pin. Open drain.

3

RST

Reset input pin for 3-wire operation. (See “Parasite Power” section.)

4

DQ

Data input/output pin for 3-wire operation.

5

I/O

Data input/output for 1-Wire operation: Open drain. (See “Parasite

Power” section.)

6

CLK

Clock input pin for 3-wire operation.

7,12

NC

No connection pins.

8,13

GND

Ground pin. Either pin can be used for ground.

9

V

BATB

Battery backup input pin. Battery voltage can be 2.8V to 5.5V. (See

V

BATO

pin description and “Power Control” section.)

10

V

BATO

Battery operate input pin for 2.8V to 5.5V operation. The V

CC

&

V

BATB

pins must be grounded when this pin is used to power the chip.

(See “Power Control” section.)

11

1Hz

1Hz square wave output: Open drain.

14,15

X

1

,X

2

Crystal pins. Connections for a standard 32.768kHz quartz crystal,

EPSON part number C-002RX or C-004R (be sure to request 6pF load

capacitance).

NOTE: X1 and X2 are very high impedance nodes. It is recommended

that they and the crystal be guard-ringed with ground and that high

frequency signals be kept away from the crystal area. See Figure 18 and

Application Note 58 for details.

OVERVIEW

The DS2404 has four main data components: 1) 64-bit lasered ROM, 2) 256-bit scratchpad, 3) 4096-bit

SRAM, and 4) timekeeping registers. The timekeeping section utilizes an on-chip oscillator that is

connected to an external 32.768kHz crystal. The SRAM and timekeeping registers reside in one

contiguous address space referred to hereafter as memory. All data is read and written least significant bit

first.

Two communication ports are provided a 1-Wire port and a 3-wire port. A port selector determines which

of the two ports is being used. The communication ports and the ROM are parasite-powered via I/O,

RST

, or V

CC

. This allows the ROM to be read in the absence of power. The ROM data is accessible only

through the 1-Wire port. The scratchpad and memory are accessible via either port.

If the 3-wire port is used, the master provides one of four memory function commands: 1) read memory,

2) read scratchpad, 3) write scratchpad, or 4) copy scratchpad. The only way to write memory is to first

write the scratchpad and then copy the scratchpad data to memory. (See Figure 6.)

If the 1-Wire port is used, the memory functions will not be available until the ROM function protocol

has been established. This protocol is described in the ROM functions flow chart (Figure 9). The master

must first provide one of five ROM function commands: 1) read ROM, 2) match ROM, 3) search ROM,