Serial-interface cascade timing, Example of serial-interface cascade timing – Rainbow Electronics MAX6975 User Manual

Page 19

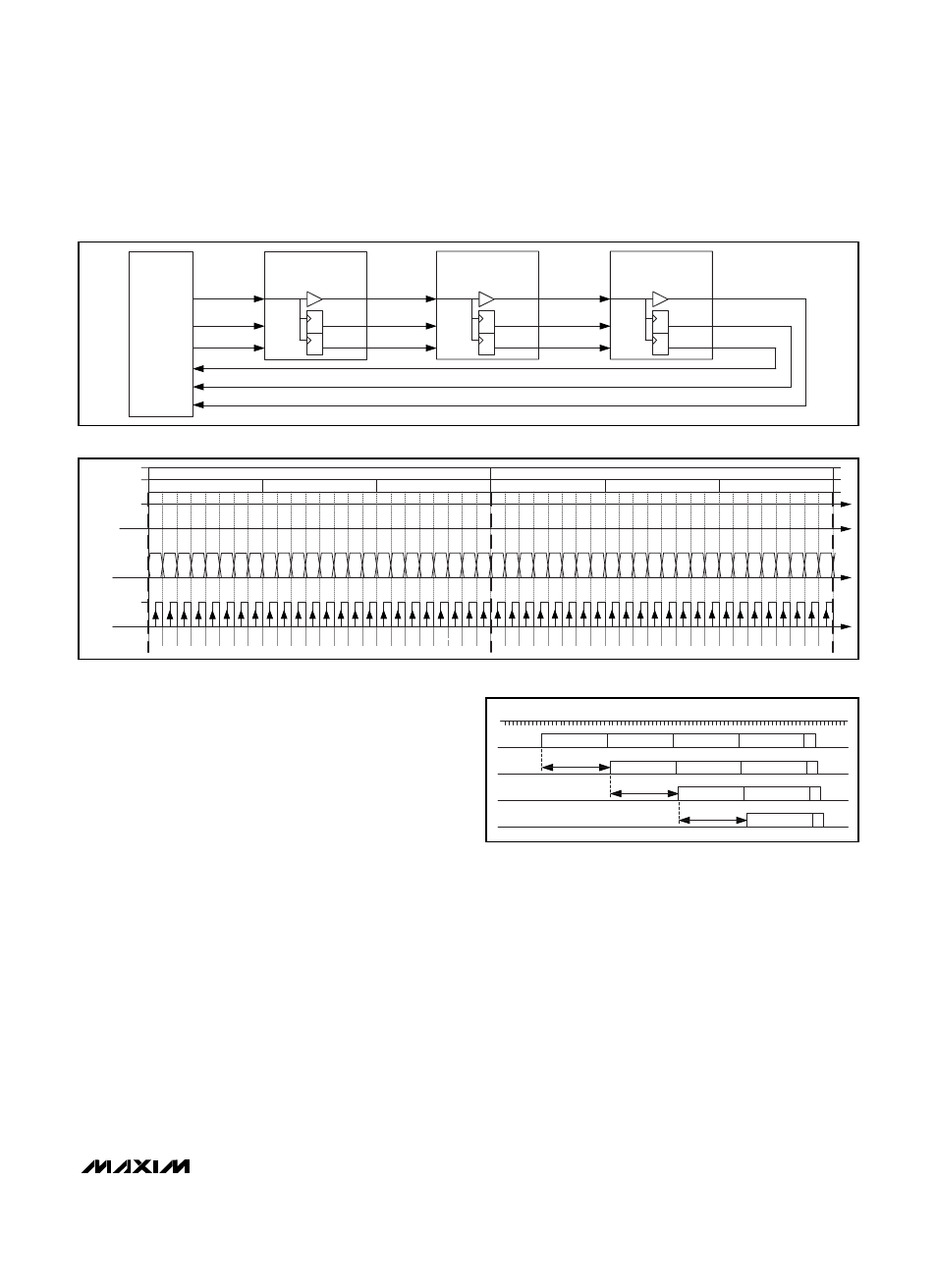

Serial-Interface Cascade Timing

The MAX6974/MAX6975 serial-interface protocol timing

is simplified by the guaranteed setup and hold charac-

teristics of the outputs from one device driving the

inputs of another. An example of a cascade of three

MAX6974/MAX6975 devices is shown in

Figure

8.

Example of Serial-Interface

Cascade Timing

The basic timing of a MAX6974/MAX6975 cascaded

chain of three devices demonstrates the principle that

applies to any number of cascaded devices. The first

device connected to the host transmitter is referenced

as 1, and the remaining devices are referenced as 2

and 3. Device 3 outputs connect to the host for commu-

nicating diagnostic and fault counter data.

The first MAX6974/MAX6975, device 1, receives the

header and captures the first set of data bits. The

number of captured bits is determined by the command

given in the header. A timing example of the data trans-

fer for the Load CALDAC command is shown in Figure

9. Device 1 does not send the captured data out on

DOUT. Instead, device 1 sends out a new header 25

clock cycles after the reception of the first header bit on

DIN. The data flow on each interconnect node is shown

in

Figure

10.

After capturing the first data set, device 1 transmits all

following data segments and the optional tail segment

on DOUT, delayed by one CLKI cycle. Device 2

receives the new header from device 1, followed by

data that now begins with device 2’s data set. Device 2

repeats the same process as described above; captur-

ing the first data set received, appending a new head-

er, and passing all subsequent data out DOUT to the

next device 3. Device 3 captures the last data set and

transmits a header followed by the tail segment. The

last header and tail segments are clocked back into the

host receiver. The header received by the host contains

the updated fault counter data. The tail data bit pattern

can be compared to the tail data originally transmitted

by the host for data integrity check.

MAX6974/MAX6975

24-Output PWM LED Drivers

for Message Boards

______________________________________________________________________________________

19

HOST

CLKO

DOUT

LOADO

CLKI

DIN

LOADI

CLK0

D0

LOAD0

CLK1

D1

LOAD1

CLK2

D2

LOAD2

CLK3

D3

LOAD3

MAX6974/MAX6975

1

MAX6974/MAX6975

2

MAX6974/MAX6975

3

CLKI

DIN

LOADI

CLKO

DOUT

LOADO

CLKI

DIN

LOADI

CLKO

DOUT

LOADO

CLKI

DIN

LOADI

CLKO

DOUT

LOADO

Figure 8. Example Showing Three-Device Cascade Connection Scheme with the Interconnecting Nodes Labeled for Clarity

DATA: CALDAC DATA 1

(CONTINUOUS)

25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72

CLKI

LOADI

DIN

0

1

B CALDAC

G CALDAC

G CALDAC

B CALDAC

G CALDAC

R CALDAC

DATA: CALDAC DATA 2

D7 D6 D5 D4 D3 D2 D1 D0 D7 D6 D5 D4 D3 D2 D1 D0 D7 D6 D5 D4 D3 D2 D1 D0 D7 D6 D5 D4 D3 D2 D1 D0 D7 D6 D5 D4 D3 D2 D1 D0 D7 D6 D5 D4 D3 D2 D1 D0

Figure 9. Timing Example Showing CALDAC Data Set for the First Two Cascaded Devices

IDLE

IDLE

IDLE

IDLE

CLK0

3 BYTES 1

3 BYTES 2

3 BYTES 3

HEADER 1

T

3 BYTES 2

3 BYTES 3

HEADER 2

T

3 BYTES 3

HEADER 3

T

HEADER 4

T

25 CLOCKS

25 CLOCKS

25 CLOCKS

D0

D1

D2

D3

Figure 10. Data Cascading Example for 24-Bit Data Words