Output pwm led drivers for message boards – Rainbow Electronics MAX6975 User Manual

Page 16

MAX6974/MAX6975

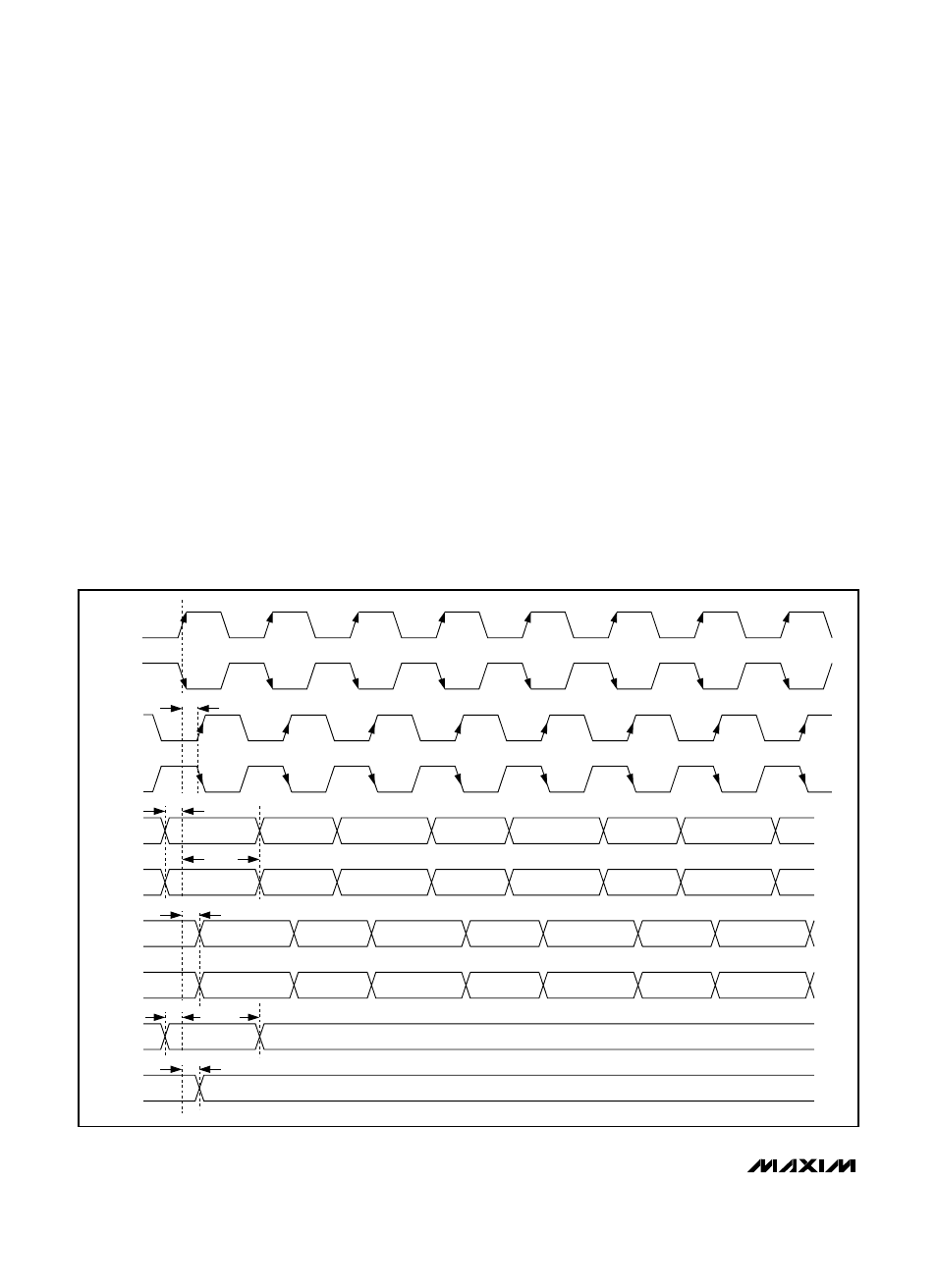

The serial interface uses the continuously running

clock, CLKI, to synchronously transfer and latch data

(33MHz max). The MAX6974/MAX6975 sample inputs

DIN and LOADI on the rising edge of CLKI and update

outputs DOUT and LOADO on the rising edge of CLKI.

The MAX6974/MAX6975 specifications guarantee that

cascaded devices observe setup and hold timing from

device to device, making external buffers and clock

trees unnecessary, even in very large systems.

The high-speed CLKI, CLKO, DIN, and DOUT signals

use low-voltage differential signaling (LVDS), and the

less frequently changing control signals, LOADI and

LOADO, use standard CMOS. The differential signals

are generally referred to in unipolar shorthand; for

example, the statement “CLKI rising edge” means that

CLKI+ is rising, and CLKI- is falling.

The MAX6974/MAX6975 use LVDS drivers with differential

signaling (300mV nominal logic swing around a +1.2V

bias) and cascaded CMOS control signals to minimize

signal-path EMI and simplify interface timing and PC

board layout. Note the differential inputs for the first dri-

ver can be driven from +3.3V CMOS using LVDS level

translators, such as the MAX9112 terminated with 110Ω

(see Figure 12).

A 25MHz to 33MHz clock frequency is recommended

to keep the display refresh rate high. When using the

MAX6975 in reduced global-intensity mode (GLB4 = 1

in configuration register), the recommended clock

frequency range is 6MHz to 33MHz.

Serial-Interface Protocol Structure

The MAX6974/MAX6975 serial interface transfers all

data and control functions using a protocol structure

consisting of header, data, and optional tail segments

transmitted in this sequence. The header and tail

24-Output PWM LED Drivers

for Message Boards

16

______________________________________________________________________________________

t

HD-DIN

t

HD-LOADI

CLKI+

CLKI-

CLKO+

CLKO-

DIN+

DIN-

DOUT+

DOUT-

LOADI

LOADO

t

PD-CLKO

t

SU-DIN

t

PD-DOUT

t

PD-LOADO

t

SU-LOADI

Figure 6. Serial-Interface Timing