Wire spi bus – Rainbow Electronics MAXQ7670 User Manual

Page 24

MAXQ7670

Microcontroller with 10-Bit ADC,

PGA, 64KB Flash, and CAN Interface

24

______________________________________________________________________________________

The TAP controller communicates synchronously with

the host system (bus master) through four digital I/Os:

test mode select (TMS), test clock (TCK), test data

input (TDI), and test data output (TDO). The internal

TAP module consists of several shift registers and a

TAP controller (see Figure 11). The shift registers serve

as transmit-and-receive data buffers for a debugger.

4-Wire SPI Bus

The MAXQ7670 includes a powerful hardware SPI mod-

ule, providing serial communication with a wide variety

of external devices. The SPI port on the MAXQ7670 is a

fully independent module that is accessed through soft-

ware. This full 4-wire, full-duplex serial bus module sup-

ports master and slave modes. The SPI clock

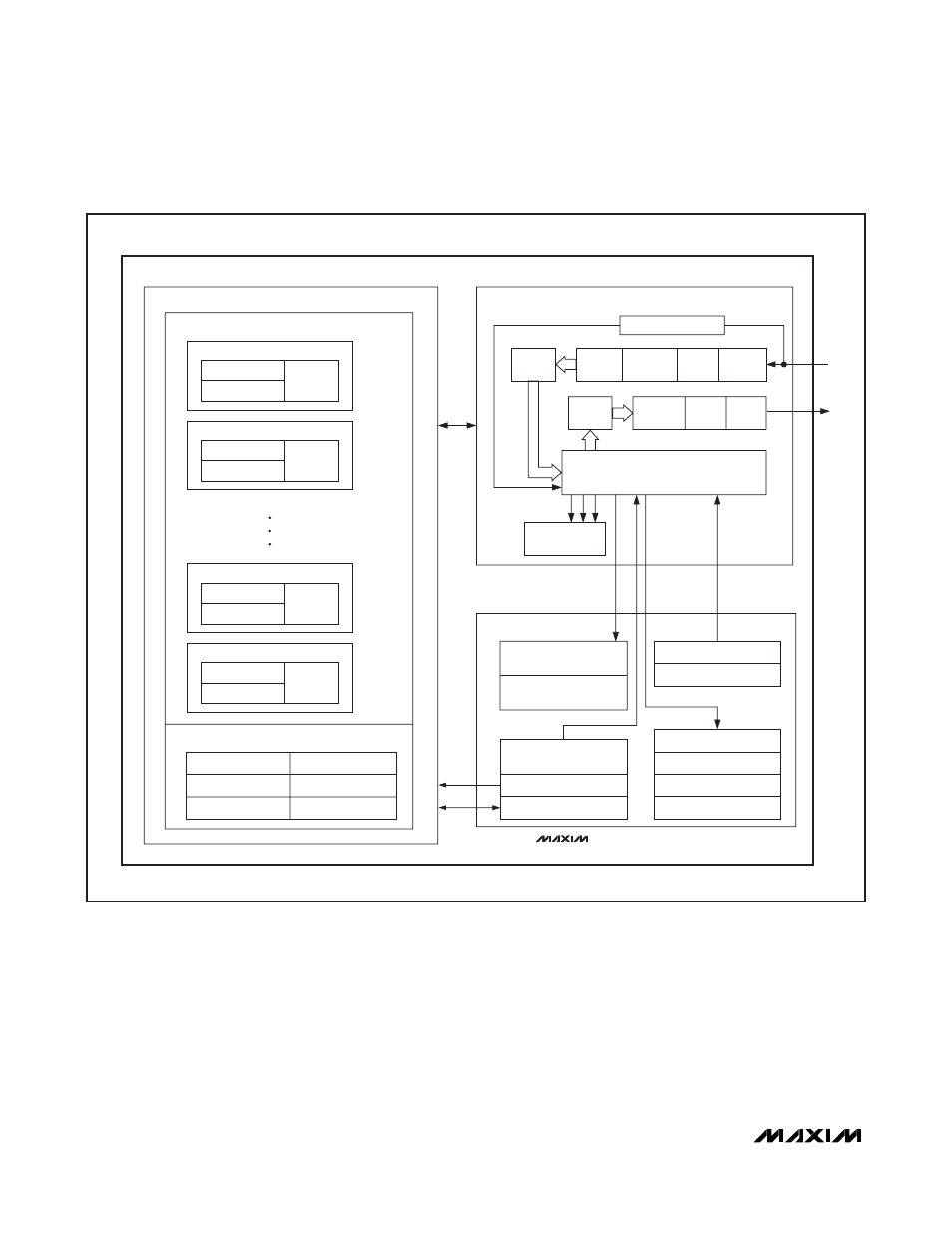

CAN 0 CONTROLLER BLOCK DIAGRAM

DUAL PORT MEMORY

CAN PROCESSOR

CAN 0 PERIPHERAL REGISTERS

MESSAGE CENTERS 1–15

BUS ACTIVITY WAKE-UP

8-BIT

Rx

CRC

CHECK

BIT

DESTUFF

Rx

SHIFT

BIT

TIMING

CANRXD

CANTXD

MESSAGE CENTER 2

ARBITRATION 0–3

FORMAT

DATA 0–7

MESSAGE CENTER 1

ARBITRATION 0–3

FORMAT

DATA 0–7

MESSAGE CENTER 15

CONTROL/STATUS/MASK REGISTERS

ARBITRATION 0–3

MEDIA ARBITRATION 0–1

EXT GLOBAL MASK 0–3

MEDIA ID MASK 0–1

STD GLOBAL MASK 0–1

BUS TIMING 0–1

MSG15 MASK 0–3

FORMAT

DATA 0–7

MESSAGE CENTER 14

ARBITRATION 0–3

FORMAT

DATA 0–7

CAN 0 TRANSMIT MSG ACK

CAN 0 INTERRUPT REGISTER

CAN 0 STATUS REGISTER

CAN 0 RECEIVE MSG ACK

CAN 0 OPERATION CONTROL

CAN 0 CONTROL REGISTER

CAN 0 DATA POINTER

CAN 0 MESSAGE 1–15

CONTROL REGISTERS

CAN 0 DATA BUFFER

CAN 0 TRANSMIT ERROR

COUNTER

CAN 0 RECEIVE ERROR

COUNTER

CAN INTERRUPT

SOURCES

8-BIT

Tx

CRC

GENERATE

CAN

PROTOCOL

FSM

BIT

STUFF

Tx

SHIFT

MAXQ7670

Figure 9. CAN 0 Controller Block Diagram