Table 4-1, Bit definitions for the status byte register, Remote interface reference – American Magnetics 4Q06125PS-430 High Stability Integrated Power Supply System User Manual

Page 120

102

Rev. 5

Remote Interface Reference

SCPI Status System

messages in the output buffers will clear the appropriate “Message Available”

bit. The bit definitions for the Status Byte register are defined in Table 4-1.

Bit 2 of the Status Byte register, indicating a quench condition, remains set

until the quench condition is cleared via the front panel or by remote

command. Bits 3 and 4 remain set until all data has been read from the

respective output buffer.

The Status Byte condition register is cleared when:

•

A

*CLS

command is executed.

•

The Standard Event register is read (only bit 5 of the Status Byte

register is cleared).

•

The indicated condition no longer exists.

The Status Byte enable register is cleared when:

•

The

*SRE 0

command is executed.

•

The power is turned off and then back on, and the Model 430

Programmer was configured for

*PSC 1

(power-on status clear).

The enable register setting is persistent if the Model 430

Programmer is configured for

*PSC 0

(no status clear on power-

on).

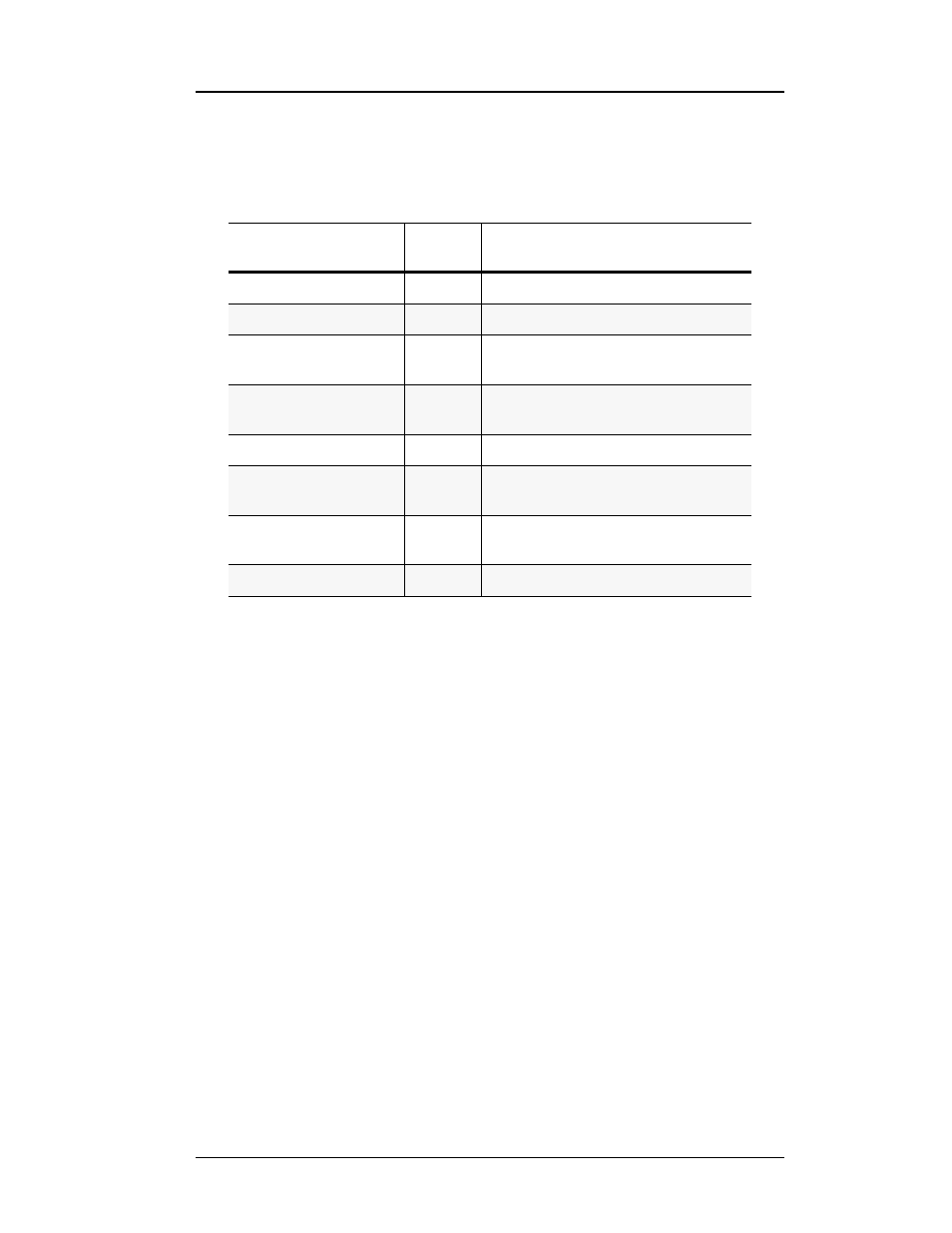

Table 4-1.

Bit Definitions for the Status Byte Register

Bit Number

Decimal

Value

Definition

0

Not Used

1

Always “0”.

1

Not Used

2

Always “0”.

2 Quench Condition

4

The Model 430 has detected a

quench.

3 Serial Message

Available

8

The serial output buffer contains

unread data.

4

Not Used

16

Always “0”.

5 Standard Event

32

One or more enabled bits are set in

the Standard Event register.

6 Status Byte

Summary

64

One or more enabled bits are set in

the Status Byte register.

7

Not Used

128

Always “0”.