Data(byte) ordering – VXI TECHNOLOGY SVM2608 User Manual

Page 30

VXI Technology, Inc.

30

SVM2608 Programming

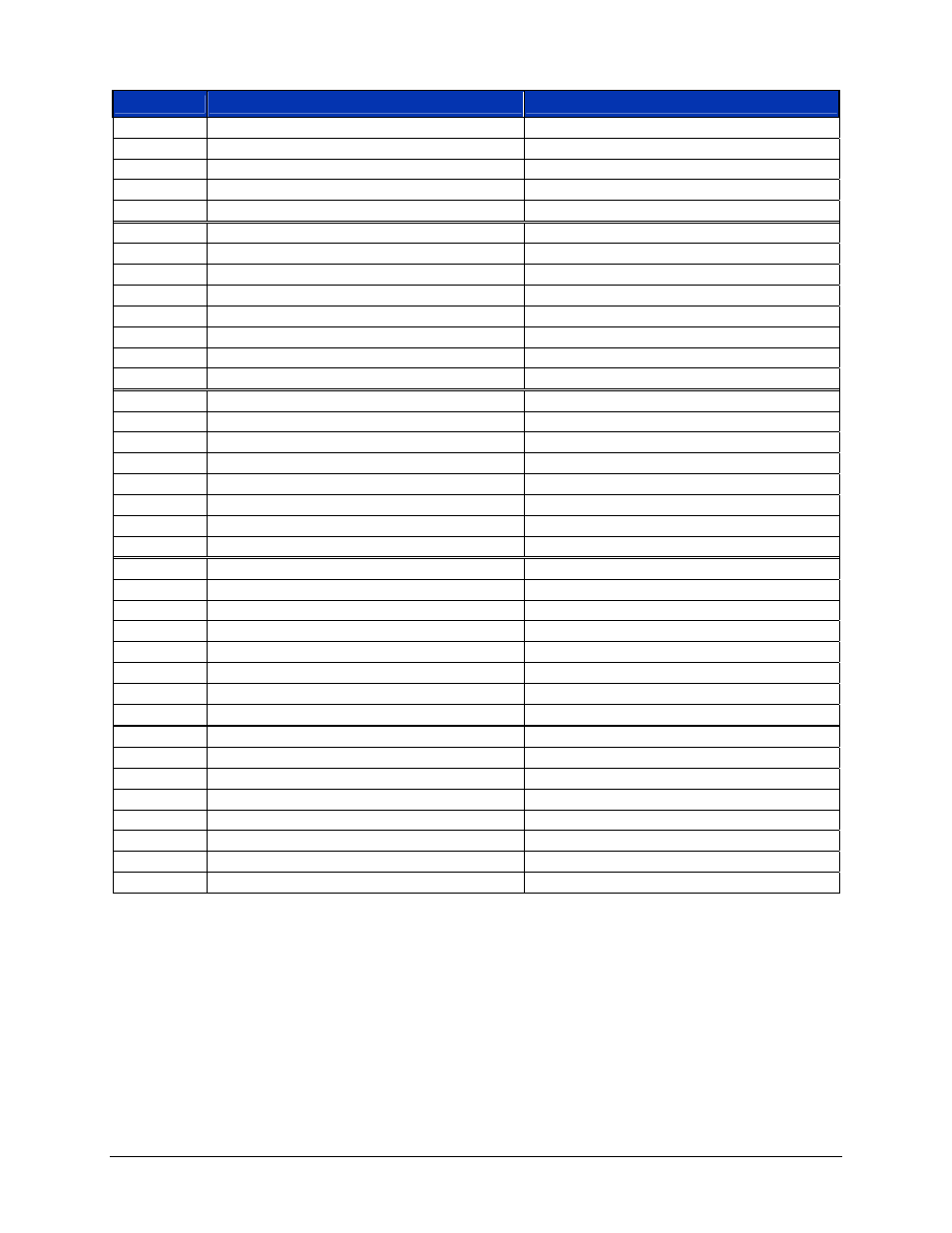

OFFSET

WRITE FUNCTION

READ FUNCTION

0xB6

Pre-Trigger Points (Channel 4) – (LS)

Pre-Trigger Points (Channel 4) – (LS)

0xB8

Trigger Delay (Channel 4) – (MS)

Trigger Delay (Channel 4) – (MS)

0xBA

Trigger Delay (Channel 4) – (LS)

Trigger Delay (Channel 4) – (LS)

0xBC

0xBE

0xC0

Reserved

0xC2

0xC4

Reserved

0xC6

Reserved

0xC8

Reserved

Result Register (Channel 4) – (MS)

0xCA

Reserved

Result Register (Channel 4) – (LS)

0xCC

Reserved

Result Register (Channel 4) – (MS)

0xCE

Reserved

Result Register (Channel 4) – (LS)

0xD0

0xD2

0xD4

Sample Rate (Channel 5) – (MS)

Sample Rate (Channel 5) – (MS)

0xD6

Sample Rate (Channel 5) – (LS)

Sample Rate (Channel 5) – (LS)

0xD8

Sample Points (Channel 5) – (MS)

Sample Points (Channel 5) – (MS)

0xDA

Sample Points (Channel 5) – (LS)

Sample Points (Channel 5) – (LS)

0xDC

Pre-Trigger Points (Channel 5) – (MS)

Pre-Trigger Points (Channel 5) – (MS)

0xDE

Pre-Trigger Points (Channel 5) – (LS)

Pre-Trigger Points (Channel 5) – (LS)

0xE0

Trigger Delay (Channel 5) – (MS)

Trigger Delay (Channel 5) – (MS)

0xE2

Trigger Delay (Channel 5) – (LS)

Trigger Delay (Channel 5) – (LS)

0xE4

0xE6

0xE8

Reserved

0xEA

0xEC

Reserved

0xEE

Reserved

0xF0

Reserved

Result Register (Channel 5) – (MS)

0xF2

Reserved

Result Register (Channel 5) – (LS)

0xF4

Reserved

Result Register (Channel 5) – (MS)

0xF6

Reserved

Result Register (Channel 5) – (LS)

0xF8 Reserved

Reserved

0xFA Reserved

Reserved

0xFC Reserved

Reserved

0xFE

External Trigger Level for High-Speed Channel External Trigger Level for High-Speed Channel

D

ATA

(B

YTE

)

O

RDERING

When a pair of 16-bit registers is read as a 32-bit register, the content of the register marked MS is

placed on the VME Bus on D31 - D16 and the content of the register marked LS is placed on

D15 - D0. Similarly, when a pair of 16-bit registers is written as a 32-bit register, the register

marked MS is loaded with the data present on the VME Bus on D31 - D16 and the register marked

LS is loaded with the data present on D15 - D0. All other registers should be addressed as 16-bit

registers to prevent any malfunctioning.