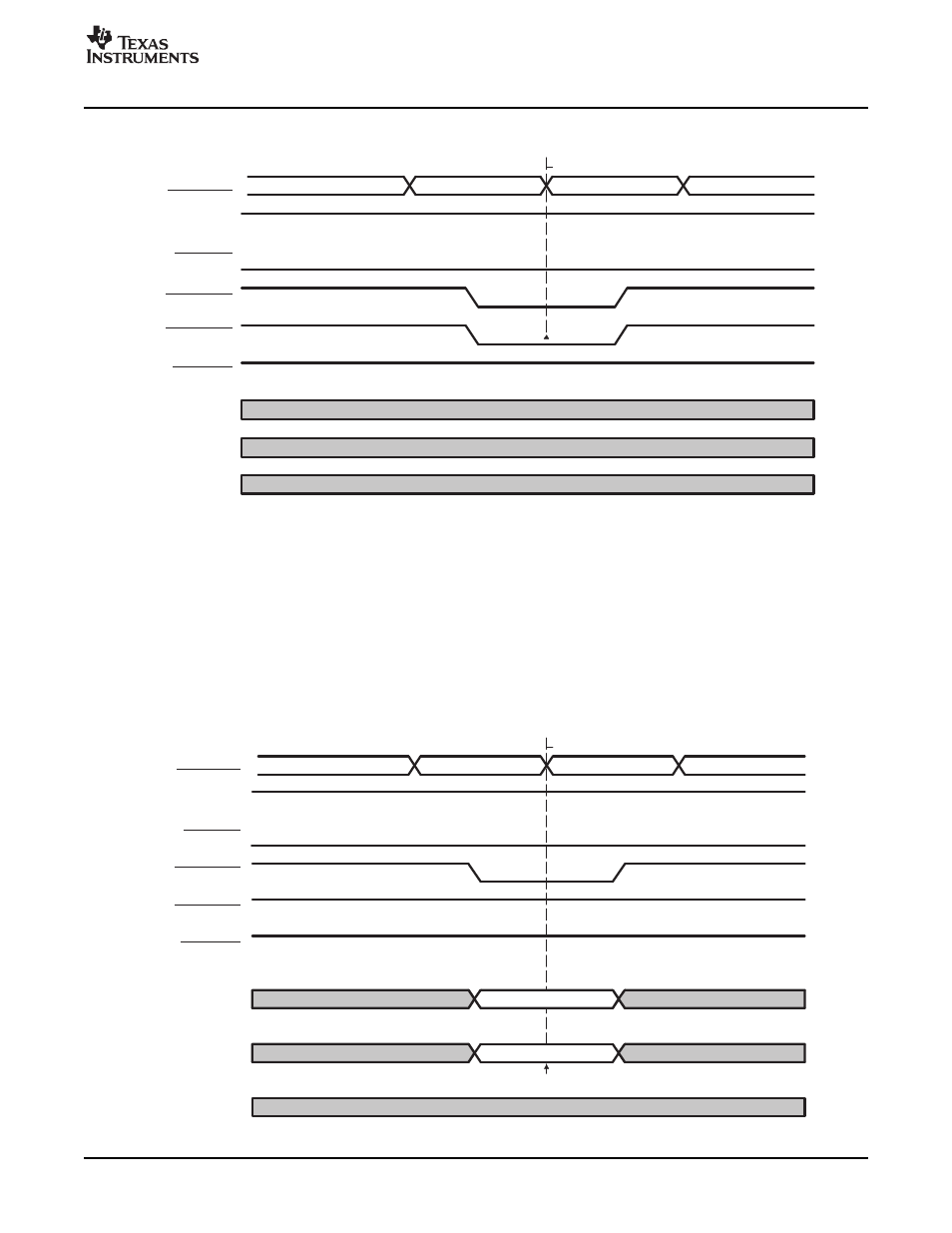

3 activation (actv), Figure 4 – Texas Instruments DM648 DSP User Manual

Page 15

www.ti.com

REFR

DDR_CLK

DDR_CLK

DDR_CS

DDR_CKE

DDR_RAS

DDR_WE

DDR_DQM[3:0]

DDR_CAS

DDR_BA[2:0]

DDR_A[13:0]

2.4.3

Activation (ACTV)

ACTV

BANK

ROW

DDR_CLK

DDR_CLK

DDR_CS

DDR_CKE

DDR_RAS

DDR_WE

DDR_DQM[3:0]

DDR_CAS

DDR_BA[2:0]

DDR_A[13:0]

Peripheral Architecture

Figure 4. Refresh Command

The DDR2 memory controller automatically issues the activate (ACTV) command before a read or write to

a closed row of memory. The ACTV command opens a row of memory, allowing future accesses (reads or

writes) with minimum latency. The value of DDR_BA[2:0] selects the bank and the value of A[12:0] selects

the row. When the DDR2 memory controller issues an ACTV command, a delay of t

RCD

is incurred before

a read or write command is issued.

shows an example of an ACTV command. Reads or writes to

the currently active row and bank of memory can achieve much higher throughput than reads or writes to

random areas because every time a new row is accessed, the ACTV command must be issued and a

delay of t

RCD

incurred.

Figure 5. ACTV Command

SPRUEK5A – October 2007

DSP DDR2 Memory Controller

15