Transcend Information CompactFlash CF 300X User Manual

Page 26

T

T

T

S

S

S

2

2

2

G

G

G

~

~

~

1

1

1

6

6

6

G

G

G

C

C

C

F

F

F

3

3

3

0

0

0

0

0

0

300X CompactFlash Card

Transcend Information Inc.

V1.1

26

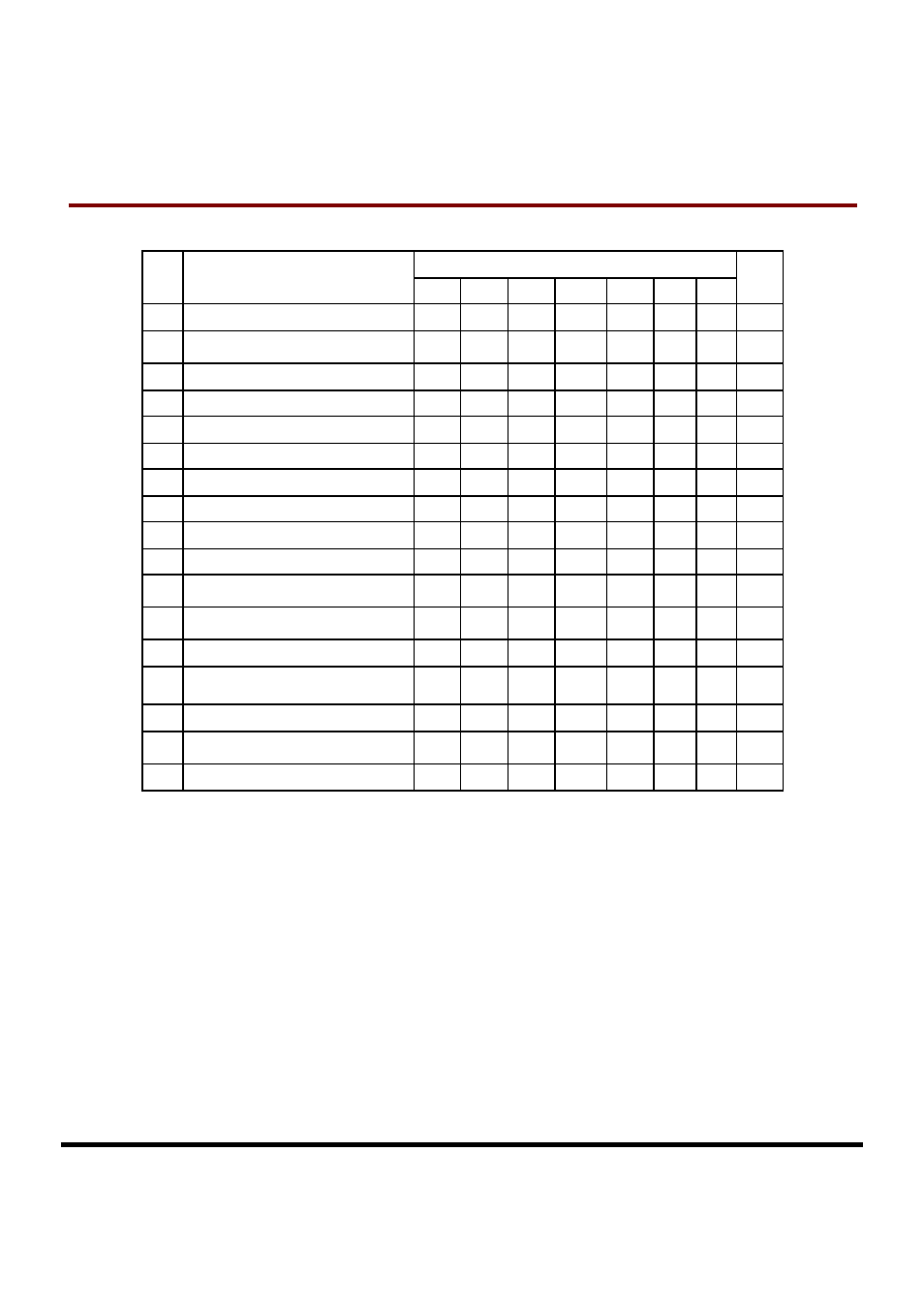

True IDE PIO Mode Read/Write Timing Specification

Mode

Item

0

1

2

3

4

5

6

Note

t0

Cycle time (min)

600

383

240

180

120

100

80

1

t1

Address Valid to -IORD/-IOWR

setup (min)

70

50

30

30

25

15

10

t2

-IORD/-IOWR (min)

165

125

100

80

70

65

55

1

t2

-IORD/-IOWR (min) Register (8 bit)

290

290

290

80

70

65

55

1

t2i

-IORD/-IOWR recovery time (min)

-

-

-

70

25

25

20

1

t3

-IOWR data setup (min)

60

45

30

30

20

20

15

t4

-IOWR data hold (min)

30

20

15

10

10

5

5

t5

-IORD data setup (min)

50

35

20

20

20

15

10

t6

-IORD data hold (min)

5

5

5

5

5

5

5

T6Z -IORD data tristate (max)

30

30

30

30

30

20

20

2

t7

Address valid to -IOCS16 assertion

(max)

90

50

40

n/a

n/a

n/a

n/a

4

t8

Address valid to -IOCS16 released

(max)

60

45

30

n/a

n/a

n/a

n/a

4

t9

-IORD/-IOWR to address valid hold

20

15

10

10

10

10

10

tRD

Read Data Valid to IORDY active

(min), if IORDY initially low after tA

0

0

0

0

0

0

0

tA

IORDY Setup time

35

35

35

35

35

na

5

na

5

3

tB

IORDY Pulse Width (max)

125

0

1250 1250 1250 1250 na

5

na

5

tC

IORDY assertion to release (max)

5

5

5

5

5

na

5

na

5

Notes: All timings are in nanoseconds. The maximum load on -IOCS16 is 1 LSTTL with a 50 pF (40pF below 120nsec Cycle Time)

total load. All times are in nanoseconds. Minimum time from -IORDY high to -IORD high is 0 nsec, but minimum -IORD width

shall still be met.

1) t0 is the minimum total cycle time, t2 is the minimum command active time, and t2i is the minimum command recovery time or

command inactive time. The actual cycle time equals the sum of the actual command active time and the actual command

inactive time. The three timing requirements of t0, t2, and t2i shall be met. The minimum total cycle time requirement is

greater than the sum of t2 and t2i. This means a host implementation can lengthen either or both t2 or t2i to ensure that t0 is

equal to or greater than the value reported in the device’s identify device data. A CompactFlash Storage Card implementation

shall support any legal host implementation.

2) This parameter specifies the time from the negation edge of -IORD to the time that the data bus is no longer driven by the

CompactFlash Storage Card (tri-state).

3) The delay from the activation of -IORD or -IOWR until the state of IORDY is first sampled. If IORDY is inactive then the host

shall wait until IORDY is active before the PIO cycle can be completed. If the CompactFlash Storage Card is not driving

IORDY negated at tA after the activation of -IORD or -IOWR, then t5 shall be met and tRD is not applicable. If the

CompactFlash Storage Card is driving IORDY negated at the time tA after the activation of -IORD or -IOWR, then tRD shall

be met and t5 is not applicable.

4) t7 and t8 apply only to modes 0, 1 and 2. For other modes, this signal is not valid.

5) IORDY is not supported in this mode.