C controlled register bit map (cont.) – Renesas HD151TS207SS User Manual

Page 20

HD151TS207SS

Rev.1.00, Apr.25.2003, page 20 of 38

I

2

C Controlled Register Bit Map (cont.)

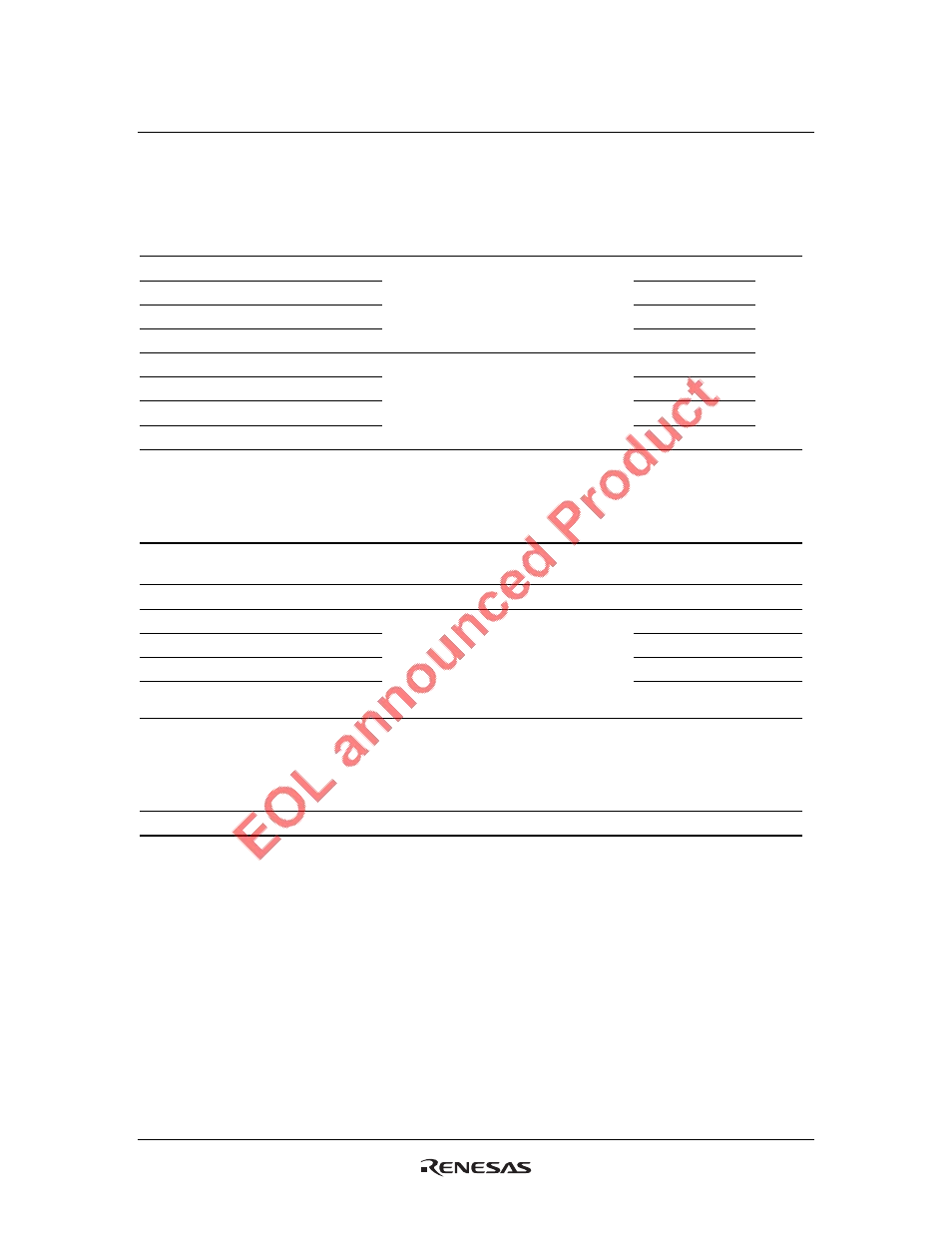

Byte22 Control Register

Bit

Description

Contents

Type

Default

Note

7

CPU Frequency Read Bit7

R

0

6

CPU Frequency Read Bit6

R

0

5

CPU Frequency Read Bit5

R

0

4

CPU Frequency Read Bit4

Calculation result of CPU frequency.

1 MHz digit

0000 = 0, 0001 = 1 …. 1001 = 9

R

0

3

CPU Frequency Read Bit3

R

0

2

CPU Frequency Read Bit2

R

0

1

CPU Frequency Read Bit1

R

0

0

CPU Frequency Read Bit0

Calculation result of CPU frequency.

0.1 MHz digit

0000 = 0, 0001 = 1 …. 1001 = 9

R

0

Byte23 Control Register

Bit

Description

Contents

Type

Default

Note

7

Watchdog Enable Control Bit

0 = Disable , Pin22 = 3V66_0 output

1 = Enable , Pin22 = RESET# output

R/W

0

6

RESET# Reverse Control Bit

0 = Normal , 1 = Reverse

R/W

0

5

Watchdog Timer Count Bit3

R/W

1

4

Watchdog Timer Count Bit2

R/W

0

3

Watchdog Timer Count Bit1

R/W

0

2

Watchdog Timer Count Bit0

These 4 bits corresponds to how

many watchdog timer will wait from

becoming “Alarm mode” (B23[0] = 1)

to outputting RESET# pin to “Low”.

Default is 586ms x8 = 4.7s at Power

ON

R/W

0

1

Backup Frequency Select Bit

0 = B10[4:0] , 1 = B11[4:0]

When SAFE_F# is “Low” , frequency

mode is changed to the predefined

frequency mode decided by B10[4:0]

or B11[4:0].

R/W

0

0

Watchdog Status Bit

0 = Normal mode, 1 = Alarm mode

R/W

0