2 mode selection and interfacing, Tda8932b, Nxp semiconductors – NXP Semiconductors TDA8932B User Manual

Page 6

TDA8932B_4

© NXP B.V. 2008. All rights reserved.

Product data sheet

Rev. 04 — 18 December 2008

6 of 48

NXP Semiconductors

TDA8932B

Class-D audio amplifier

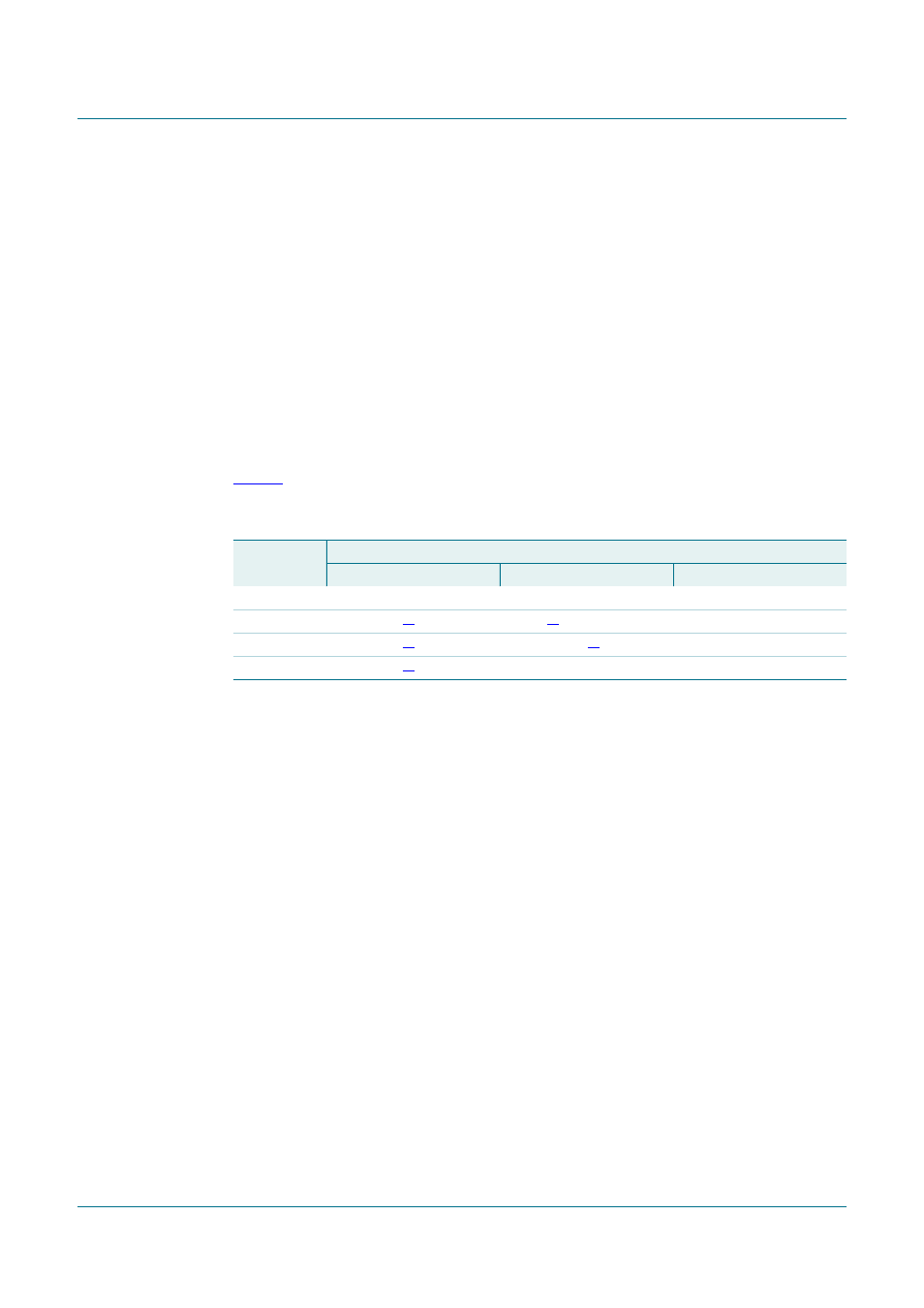

8.2 Mode selection and interfacing

The TDA8932B supports four operating modes, selected using pins POWERUP and

ENGAGE:

•

Sleep mode: with low supply current.

•

Mute mode: the amplifiers are switching idle (50 % duty cycle), but the audio signal at

the output is suppressed by disabling the Vl-converter input stages. The capacitors on

pins HVP1 and HVP2 have been charged to half the supply voltage (asymmetrical

supply only).

•

Operating mode: the amplifiers are fully operational with output signal.

•

Fault mode.

Pins POWERUP and ENGAGE are referenced to pin CGND.

shows the different modes as a function of the voltages on the POWERUP and

ENGAGE pins.

[1]

In case of symmetrical supply conditions the voltage applied to pins POWERUP and ENGAGE must never

exceed the supply voltage (V

DDA

, V

DDP1

or V

DDP2

).

If the transition between Mute mode and Operating mode is controlled via a time constant,

the start-up will be pop free since the DC output offset voltage is applied gradually to the

output between Mute mode and Operating mode. The bias current setting of the

VI-converters is related to the voltage on pin ENGAGE:

•

Mute mode: the bias current setting of the VI-converters is zero (VI-converters

disabled)

•

Operating mode: the bias current is at maximum

The time constant required to apply the DC output offset voltage gradually between Mute

mode and Operating mode can be generated by connecting a 470 nF decoupling

capacitor to pin ENGAGE.

Table 4.

Mode selection

Mode

Pin

POWERUP

ENGAGE

DIAG

Sleep

< 0.8 V

< 0.8 V

don’t care

Mute

2 V to 6.0 V

< 0.8 V

> 2 V

Operating

2 V to 6.0 V

2.4 V to 6.0 V

> 2 V

Fault

2 V to 6.0 V

don’t care

< 0.8 V