Pinning information, 1 pinning, 2 pin description – NXP Semiconductors TDA8932B User Manual

Page 4: Tda8932b, Nxp semiconductors, 1 pinning 7.2 pin description, Class-d audio amplifier

TDA8932B_4

© NXP B.V. 2008. All rights reserved.

Product data sheet

Rev. 04 — 18 December 2008

4 of 48

NXP Semiconductors

TDA8932B

Class-D audio amplifier

7.

Pinning information

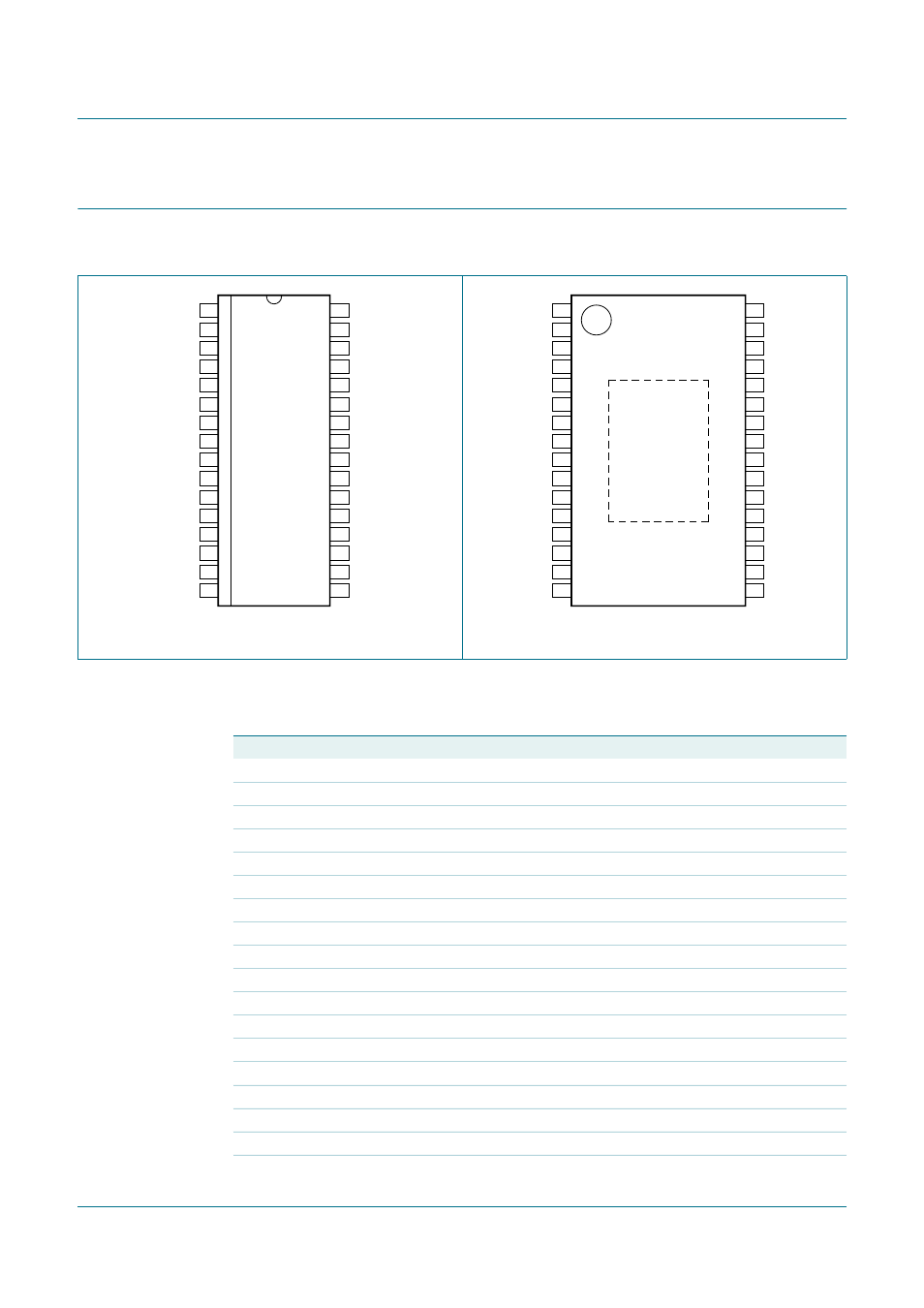

7.1 Pinning

7.2 Pin description

Fig 2.

Pin configuration SO32

Fig 3.

Pin configuration HTSSOP32

TDA8932BT

V

SSD(HW)

V

SSD(HW)

IN1P

OSCIO

IN1N

HVP1

DIAG

V

DDP1

ENGAGE

BOOT1

POWERUP

OUT1

CGND

V

SSP1

V

DDA

STAB1

V

SSA

STAB2

OSCREF

V

SSP2

HVPREF

OUT2

INREF

BOOT2

TEST

V

DDP2

IN2N

HVP2

IN2P

DREF

V

SSD(HW)

V

SSD(HW)

001aaf598

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

18

17

20

19

22

21

24

23

26

25

32

31

30

29

28

27

TDA8932BTW

V

SSD(HW)

V

SSD(HW)

IN1P

OSCIO

IN1N

HVP1

DIAG

V

DDP1

ENGAGE

BOOT1

POWERUP

OUT1

CGND

V

SSP1

V

DDA

STAB1

V

SSA

STAB2

OSCREF

V

SSP2

HVPREF

OUT2

INREF

BOOT2

TEST

V

DDP2

IN2N

HVP2

IN2P

DREF

V

SSD(HW)

V

SSD(HW)

001aaf599

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

18

17

20

19

22

21

24

23

26

25

32

31

30

29

28

27

Table 3.

Pin description

Symbol

Pin

Description

V

SSD(HW)

1

negative digital supply voltage and handle wafer connection

IN1P

2

positive audio input for channel 1

IN1N

3

negative audio input for channel 1

DIAG

4

diagnostic output; open-drain

ENGAGE

5

engage input to switch between Mute mode and Operating mode

POWERUP

6

power-up input to switch between Sleep mode and Mute mode

CGND

7

control ground; reference for POWERUP, ENGAGE and DIAG

V

DDA

8

positive analog supply voltage

V

SSA

9

negative analog supply voltage

OSCREF

10

input internal oscillator setting (only master setting)

HVPREF

11

decoupling of internal half supply voltage reference

INREF

12

decoupling for input reference voltage

TEST

13

test signal input; for testing purpose only

IN2N

14

negative audio input for channel 2

IN2P

15

positive audio input for channel 2

V

SSD(HW)

16

negative digital supply voltage and handle wafer connection

V

SSD(HW)

17

negative digital supply voltage and handle wafer connection

DREF

18

decoupling of internal (reference) 5 V regulator for logic supply