Si4421 – Silicon Laboratories SI4421 User Manual

Page 35

Si4421

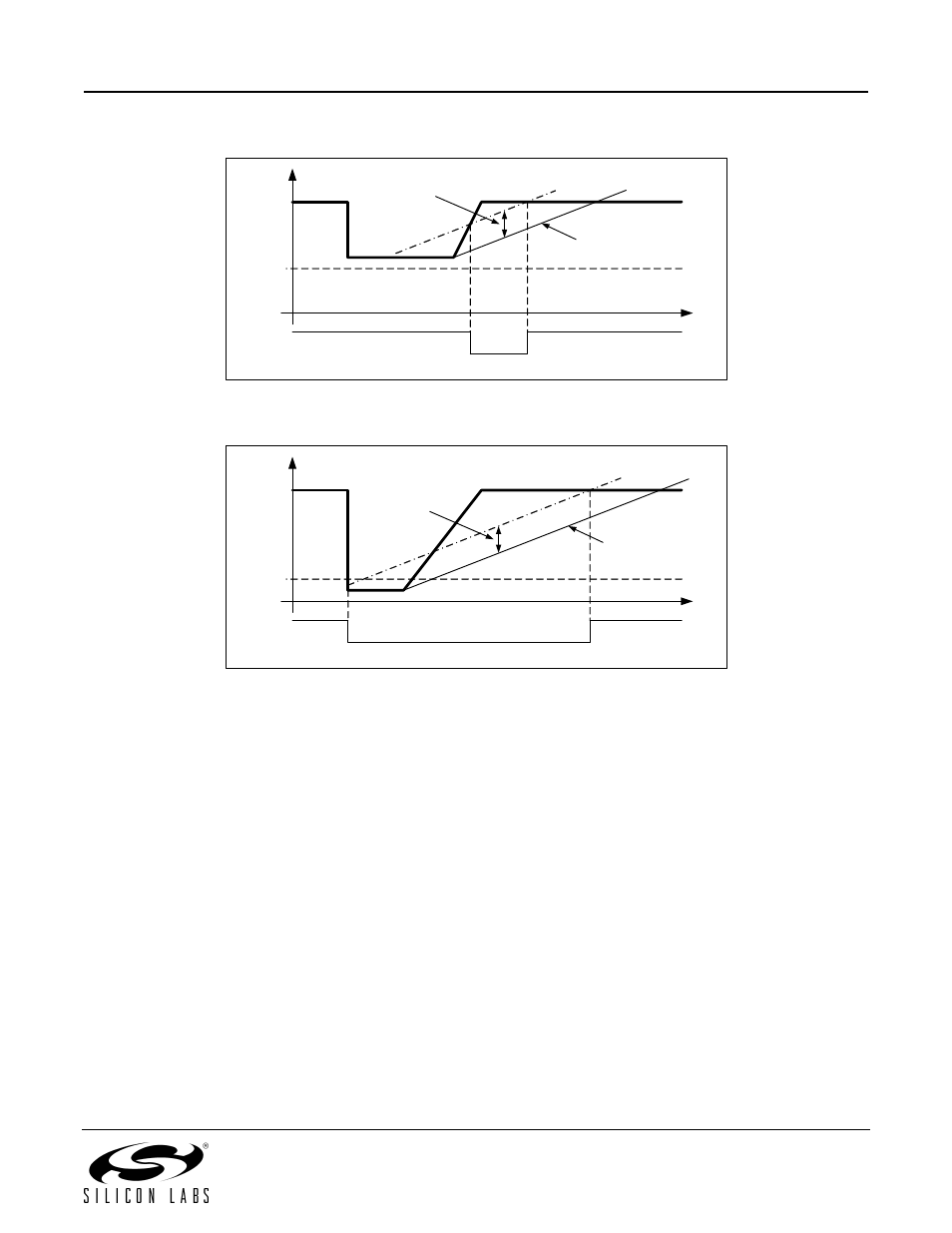

Sensitive Reset Enabled, Ripple on V

dd

:

time

V

dd

Reset threshold voltage

(600mV)

nRes

output

H

L

1.6V

Reset ramp line

(100mV/ms)

Sensitive reset disabled:

time

V

dd

Reset threshold voltage

(600mV)

nRes

output

H

L

250mV

Reset ramp line

(100mV/ms)

Software reset

Software reset can be issued by sending the appropriate control command (described at the end of the section) to the chip. The

result of the command is the same as if power-on reset was occurred but the length of the reset event is much less, 0.25ms typical.

The software reset works only when the sensitive reset mode is selected.

V

dd

line filtering

During the reset event (caused by power-on, fast positive spike on the supply line or software reset command), it is very important to

keep the V

dd

line as smooth as possible. Noise or periodic disturbing signal superimposed the supply voltage may prevent the part

getting out from reset state. To avoid this phenomenon use adequate filtering on the power supply line to keep the level of the

disturbing signal below 100mV

p-p

in the DC – 50kHz range for 200ms from V

dd

ramp start.. Typical example when a switch-mode

regulator is used to supply the radio, switching noise may be present on the V

dd

line. Follow the manufacturer’s recommendations

how to decrease the ripple of the regulator IC and/or how to shift the switching frequency.

Related control commands

FIFO and Reset Mode Command (page 20)

Setting bit<0> to high will change the reset mode to normal from the default sensitive.

SW Reset Command

Issuing FE00h command will trigger software reset (sensitive reset mode must be enabled). See the Wake-up Timer

Command (page 25).

35