Ced4h, B000h, C4f7h – Silicon Laboratories SI4421 User Manual

Page 21: Si4421, Synchron pattern command, Receiver fifo read command, Afc command

Si4421

Bit 1 (ff): FIFO fill will be enabled after synchron pattern reception. The FIFO fill stops when this bit is cleared.

Bit 0 (dr): Disables the highly sensitive RESET mode.

dr

Reset mode

Reset triggered when

0 Sensitive

reset

V

dd

below 1.6V, V

dd

glitch greater than 600mV

1 Non-sensitive

reset

V

dd

below 250mV

Note: To restart the synchron pattern recognition, bit 1 (ef, FIFO fill enable) should be cleared and set.

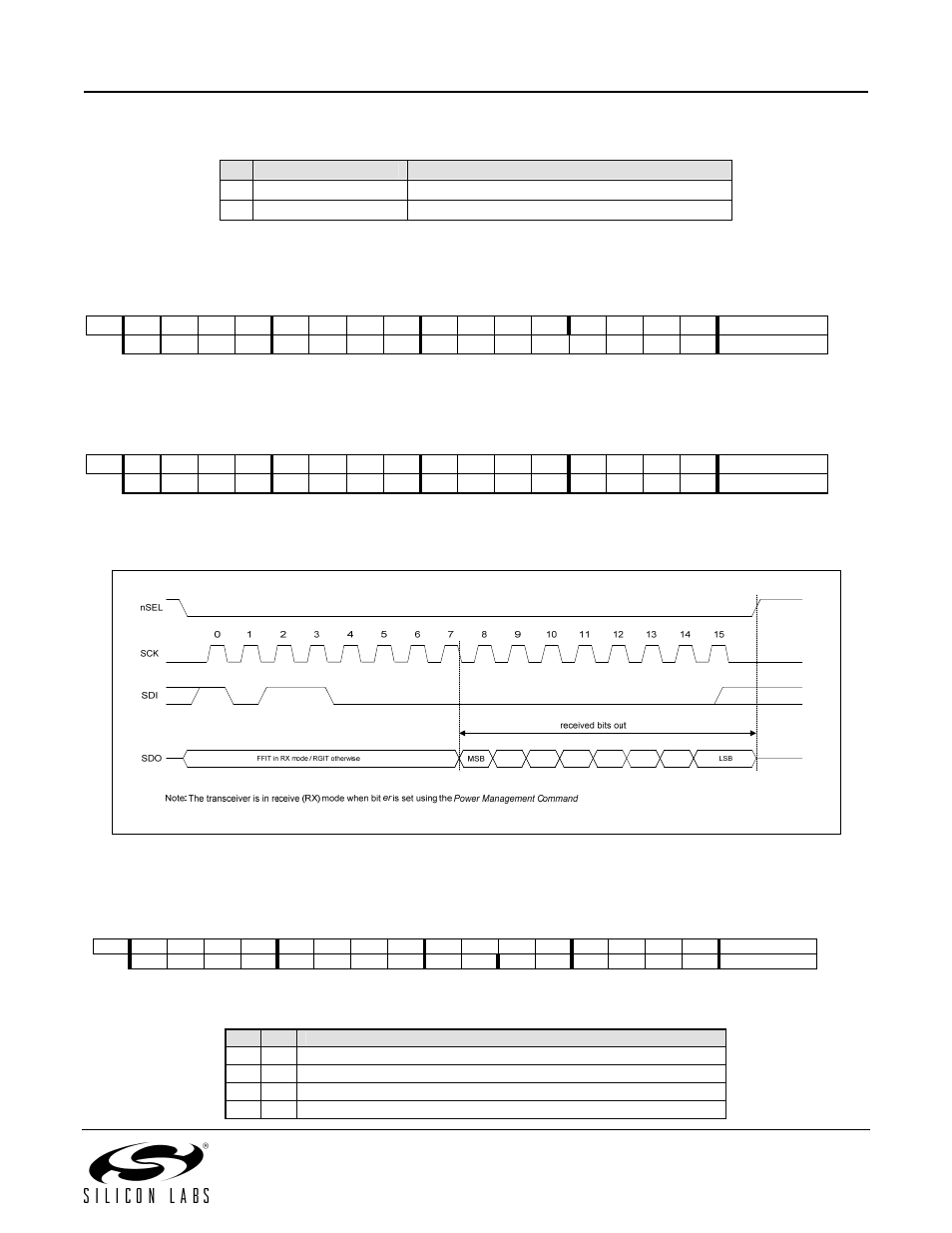

8. Synchron Pattern Command

Bit

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

POR

1 1 0 0 1 1 1 0 b7 b6 b5 b4 b3 b2 b1 b0

CED4h

The Byte0 of the synchron pattern (see FIFO and Reset Mode command, page 20) can be reprogrammed by B <b7:b0>.

9. Receiver FIFO Read Command

Bit

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

POR

1 0 1 1 0 0 0 0 0 0 0 0 0 0 0 0

B000h

With this command, the controller can read 8 bits from the receiver FIFO. Bit 6 (ef) must be set in Configuration Setting Command

(page 15).

Note: During FIFO access f

SCK

cannot be higher than f

ref

/4, where f

ref

is the crystal oscillator frequency. When the duty-cycle of the

clock signal is not 50 % the shorter period of the clock pulse width should be at least 2/f

ref

.

10. AFC Command

Bit

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

POR

1 1 0 0 0 1 0 0 a1

a0

rl1

rl0 st fi oe

en C4F7h

Bit 7-6 (a1 to a0):

Automatic operation mode selector:

a1

a0

Operation mode

0

0

Auto mode off (Strobe is controlled by microcontroller)

0

1

Runs only once after each power-up

1

0

Keep the f

offset

only during receiving (VDI=high)

1

1

Keep the f

offset

value independently from the state of the VDI signal

21