Ca80h, Si4421, Fifo and reset mode command – Silicon Laboratories SI4421 User Manual

Page 20

Si4421

Bits 2-0 (f2 to f0): DQD

threshold

parameter.

The Data Quality Detector is a digital processing part of the radio, connected to the demodulator - it is an indicator

reporting the reception of an FSK modulated RF signal. It will work every time the receiver is on. Setting this

parameter defines how clean incoming data stream would be stated as good data (valid FSK signal).

If the internally calculated data quality value exceeds the DQD threshold parameter for five consecutive data bits

for both the high and low periods, then the DQD signal goes high.

The DQD parameter in the Data Filter Command should be chosen according to the following rules:

The DQD parameter can be calculated with the following formula:

DQD

par

= 4 x (deviation – TX-RX

offset

) / bit rate

It should be larger than 4 because otherwise noise might be treated as a valid FSK signal

The maximum value is 7.

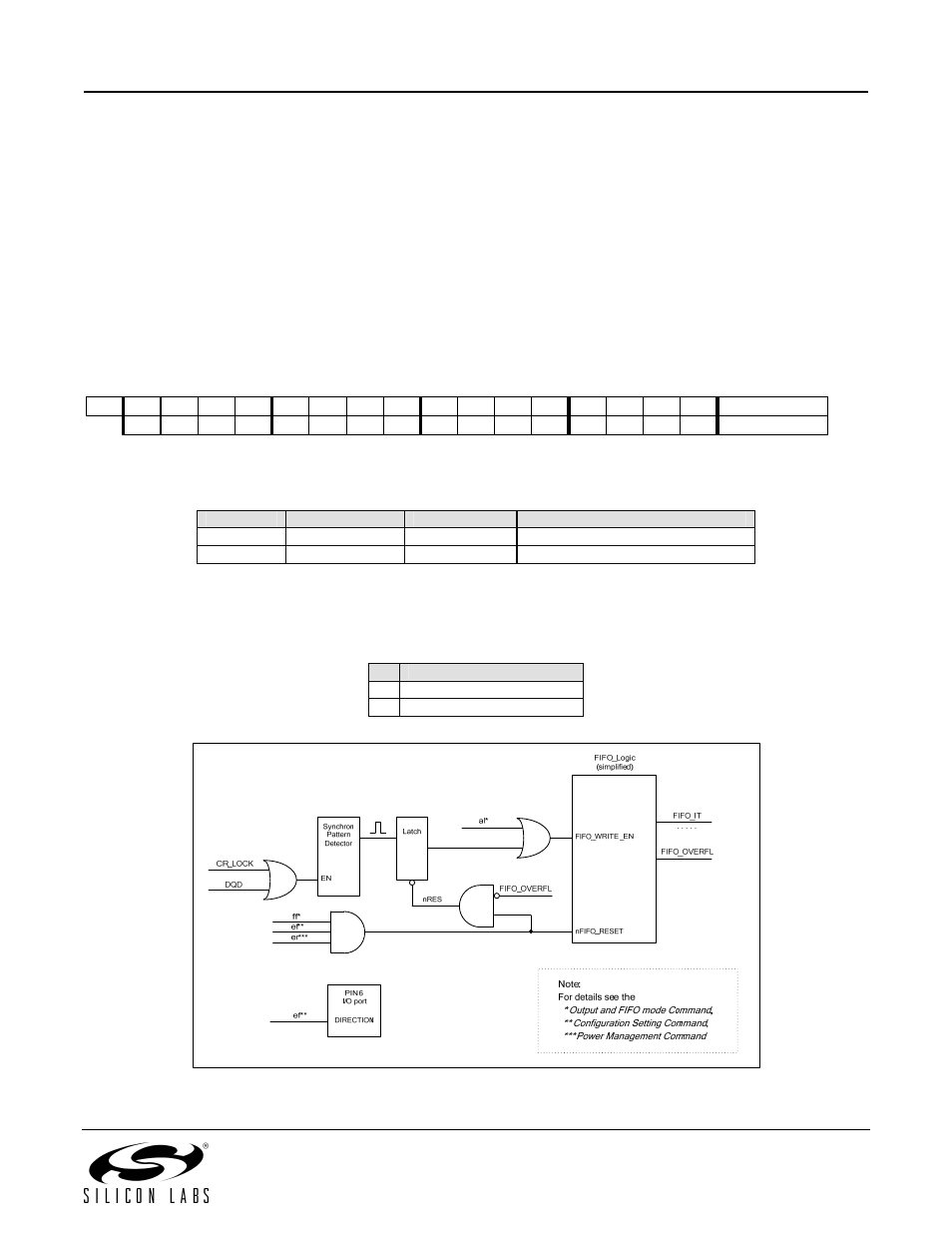

7. FIFO and Reset Mode Command

Bit

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

POR

1 1 0 0 1 0 1 0 f3 f2 f1 f0 sp al ff dr

CA80h

Bits 7-4 (f3 to f0):

FIFO IT level. The FIFO generates IT when the number of received data bits reaches this level.

Bit 3 (sp):

Select the length of the synchron pattern:

sp

Byte1

Byte0 (POR)

Synchron Pattern (Byte1+Byte0)

0 2Dh D4h

2DD4h

1 Not

used D4h

D4h

Note: The synchron pattern consists of one or two bytes depending on the sp bit. Byte1 is fixed 2Dh, Byte0 can be programmed by

the Synchron Pattern Command (page 21).

Bit 2 (al):

Set the input of the FIFO fill start condition:

al

FIFO fill start condition

0 Synchron

pattern

1 Always

fill

20