Intel PXA26X User Manual

Page 221

Intel® PXA26x Processor Family Developer’s Manual

6-31

Memory Controller

25:24

SXRA2

SX MEMORY ROW ADDRESS BIT COUNT FOR PARTITION PAIR 2/3:

00 – 12 row address bits

01 – 13 row address bits

10 – Reserved

11 – Reserved

23:21

SXRL2

RAS LATENCY FOR SX MEMORY PARTITION PAIR 2/3:

Number of external SDCLK cycles between receiving the ACT command and the READ

command. The unit size for SXRL2 is the external SDCLK cycle.

IF SXTP2 = “00” (SMROM):

000 – 1 clock

001 – 2 clocks

010 – 3 clocks

011 – 4 clocks

100 – 5 clocks

101 – 6 clocks

110 – 7 clocks

111 – 8 clocks

IF SXTP2 = 10 (non-SDRAM timing fast flash), this field is not used and must be

programmed to 111.

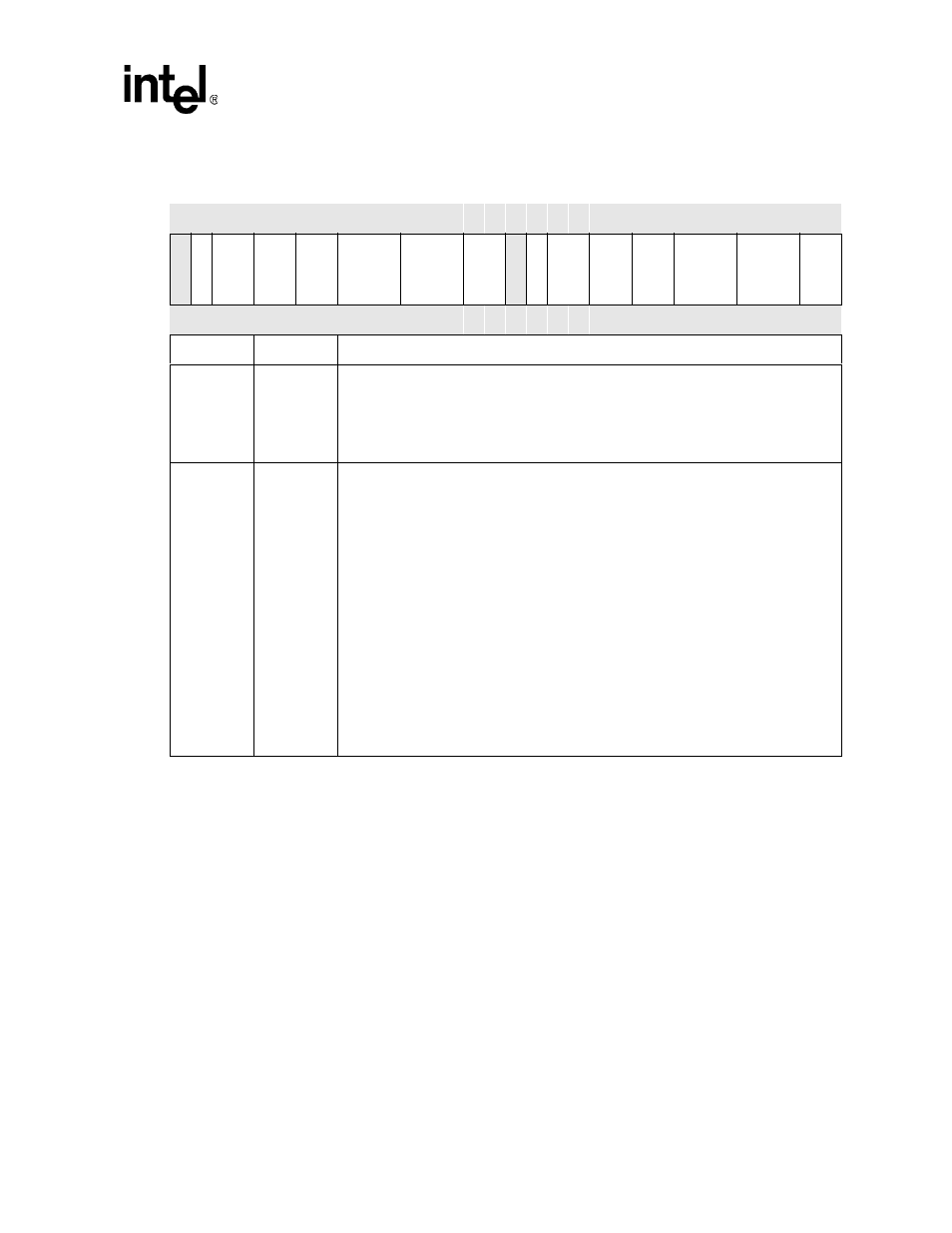

Table 6-14. SXCNFG Register Bitmap (Sheet 2 of 6)

4800 001C

SXCNFG

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

R

eser

ved

S

X

LA

TC

H

2

SXTP

2

SX

C

A

2

SX

R

A

2

SXR

L2

SXC

L2

S

XEN

2

R

eser

ved

S

X

LA

TC

H

0

SXTP

0

SX

C

A

0

SX

R

A

0

SXR

L0

SXC

L0

S

XEN

0

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

*

*

*

*

*

*

*

*

*

*

*

*

*

0

*

Bits

Name

Description