Intel GD82559ER User Manual

Page 23

Datasheet

17

Networking Silicon — GD82559ER

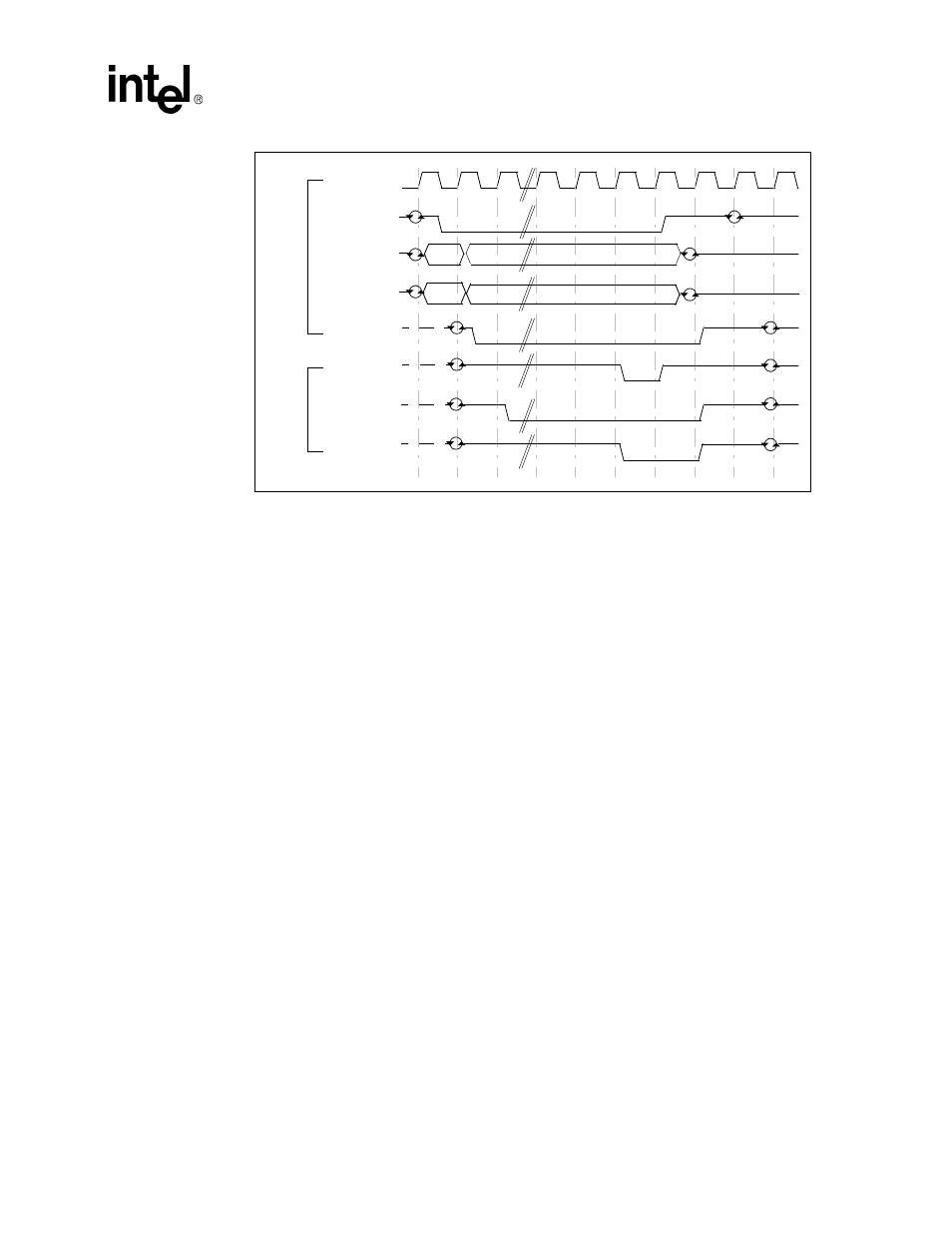

Write Accesses: The CPU, as the initiator, drives the address lines

AD[31:0],

the command and

byte enable lines

C/BE#[3:0] and

the control lines

IRDY#

and

FRAME#

. It also provides the

82559ER with valid data immediately after asserting

IRDY#

. The 82559ER controls the

TRDY#

signal and de-asserts it for a certain number of clocks until valid data is written to the Flash buffer.

By asserting

TRDY#

, the 82559ER signals the CPU that the current data access has completed.

Flash buffer write accesses can be byte length only.

4.2.1.1.3

Retry Premature Accesses

The 82559ER responds with a Retry to any configuration cycle accessing the 82559ER before the

completion of the automatic read of the EEPROM. The 82559ER may continue to Retry any

configuration accesses until the EEPROM read is complete. The 82559ER does not enforce the

rule that the retried master must attempt to access the same address again to complete any delayed

transaction. Any master access to the 82559ER after the completion of the EEPROM read will be

honored.

Figure 6

depicts the operation of a Retry cycle.

Figure 5. Flash Buffer Write Cycle

SYS

T

E

M

8

255

9E

R

CLK

FRAME#

C/BE#

IRDY#

TRDY#

DEVSEL#

AD

ADDR

MEM WR

BE#

STOP#

DATA