Revision summary – Intel UPI-C42 User Manual

Page 25

UPI-C42 UPI-L42

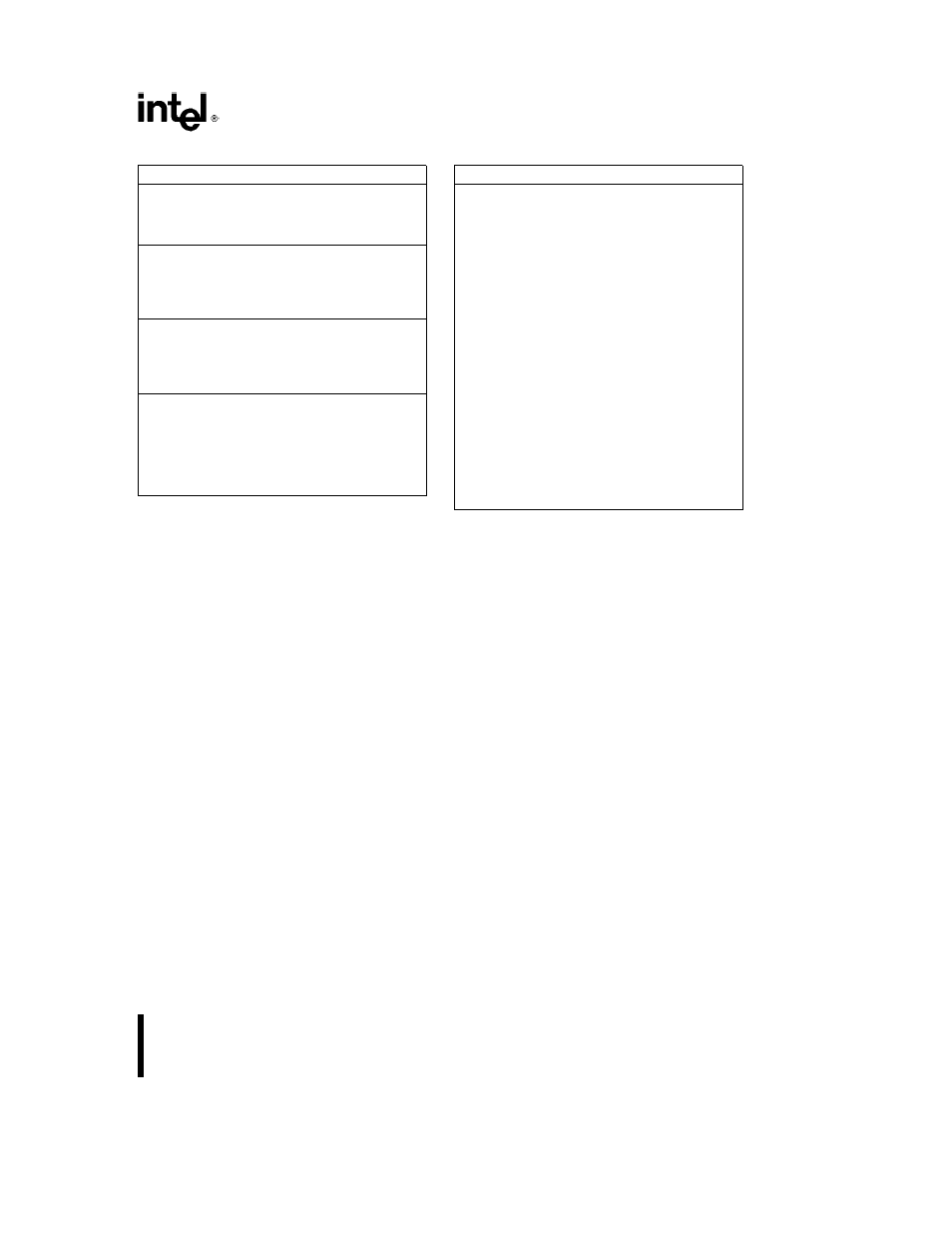

Table 4 UPI Instruction Set

(Continued)

Mnemonic

Description

Bytes

Cycles

CONTROL

(Continued)

SUSPEND

Invoke Suspend Power-

1

2

down mode

NOP

No Operation

1

1

REGISTERS

INC Rr

Increment register

1

1

INC

Rr

Increment data

1

1

memory

DEC Rr

Decrement register

1

1

SUBROUTINE

CALL addr

Jump to subroutine

2

2

RET

Return

1

2

RETR

Return and restore

1

2

status

FLAGS

CLR C

Clear Carry

1

1

CPL C

Complement Carry

1

1

CLR F0

Clear Flag 0

1

1

CPL F0

Complement Flag 0

1

1

CLR F1

Clear F1 Flag

1

1

CPL F1

Complement F1 Flag

1

1

Mnemonic

Description

Bytes

Cycles

BRANCH

JMP addr

Jump unconditional

2

2

JMPP

A

Jump indirect

1

2

DJNZ Rr addr

Decrement register

2

2

and jump

JC addr

Jump on Carry e 1

2

2

JNC addr

Jump on Carry e 0

2

2

JZ addr

Jump on A Zero

2

2

JNZ addr

Jump on A not Zero

2

2

JT0 addr

Jump on T0 e 1

2

2

JNT0 addr

Jump on T0 e 0

2

2

JT1 addr

Jump on T1 e 1

2

2

JNT1 addr

Jump on T1 e 0

2

2

JF0 addr

Jump on F0 Flag e 1

2

2

JF1 addr

Jump on F1 Flag e 1

2

2

JTF addr

Jump on Timer Flag

2

2

e

1 Clear Flag

JNIBF addr

Jump on IBF Flag

2

2

e

0

JOBF addr

Jump on OBF Flag

2

2

e

1

JBb addr

Jump on Accumula-

2

2

for Bit

UPI-C42 UPI-L42 Only

REVISION SUMMARY

The following has been changed since Revision

-003

1 Delete all references to standby power down

mode

The following has been changed since Revision

-002

1 Added information on keyboard controller prod-

uct family

2 Added I

HI

specification for the UPI-L42

The following has been changed since Revision

-001

1 Added UPI-L42 references and specification

25