2 signal properties summary, Table 2-1 signal properties, Signal properties summary – Motorola MC9S12GC-Family User Manual

Page 55: Table 2-1, Signal properties

Device User Guide — 9S12C128DGV1/D V01.05

55

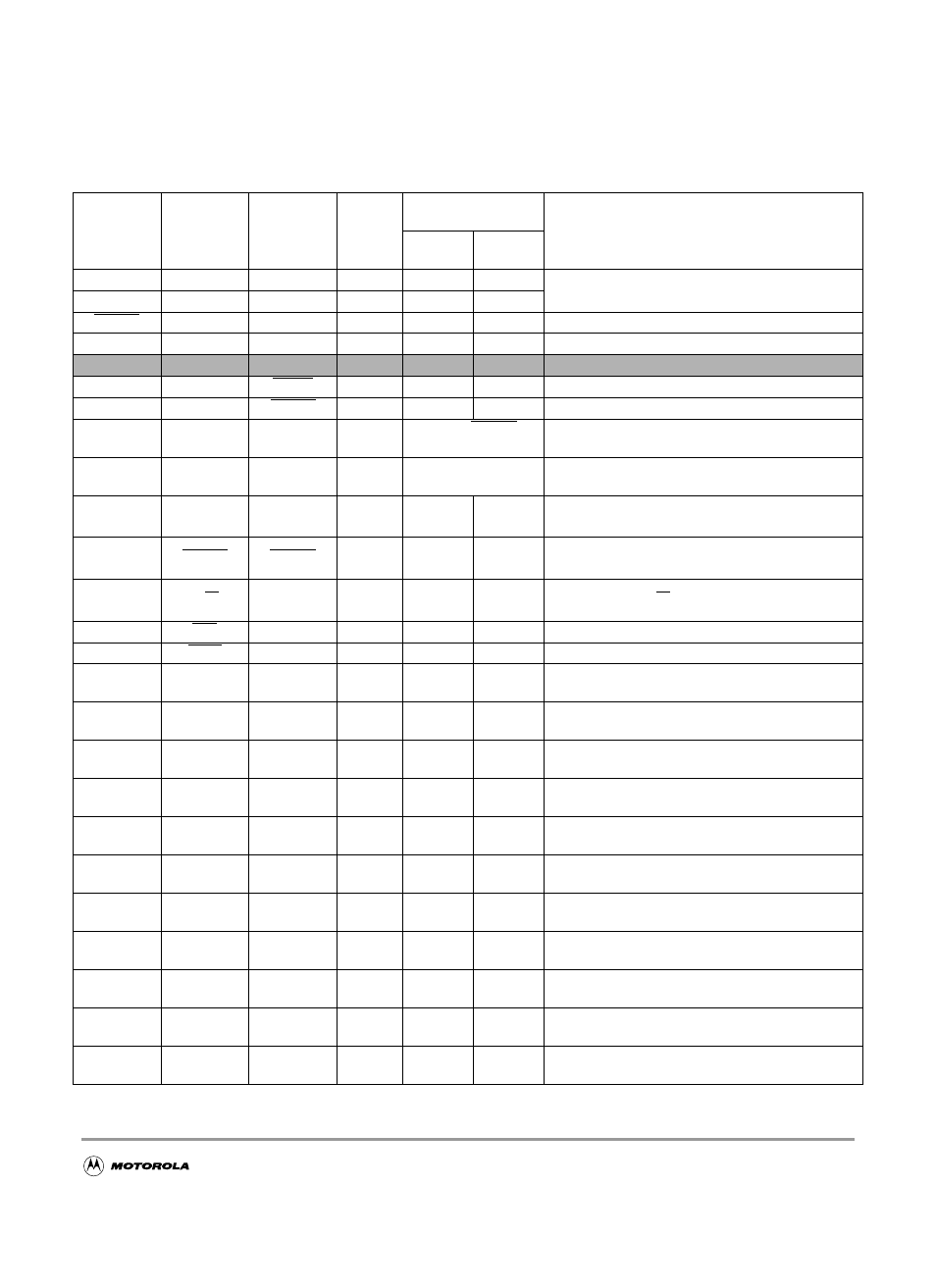

2.2 Signal Properties Summary

Table 2-1 Signal Properties

Pin Name

Function 1

Pin Name

Function 2

Pin Name

Function 3

Power

Domain

Internal Pull

Resistor

Description

CTRL

Reset

State

EXTAL

—

—

VDDPLL

NA

NA

Oscillator pins

XTAL

—

—

VDDPLL

NA

NA

RESET

—

—

VDDX

None

None

External reset pin

XFC

—

—

VDDPLL

NA

NA

PLL loop filter pin

TEST

VPP

—

VSSX

NA

NA

Test pin only

BKGD

MODC

TAGHI

VDDX

Up

Up

Background debug, mode pin, tag signal high

PE7

NOACC

XCLKS

VDDX

PUCR

Up

Port E I/O pin, access, clock select

PE6

IPIPE1

MODB

VDDX

While RESET

pin is low: Down

Port E I/O pin and pipe status

PE5

IPIPE0

MODA

VDDX

While RESET

pin is low: Down

Port E I/O pin and pipe status

PE4

ECLK

—

VDDX

PUCR

Mode

Dep

1

Port E I/O pin, bus clock output

PE3

LSTRB

TAGLO

VDDX

PUCR

Mode

Dep

Port E I/O pin, low strobe, tag signal low

PE2

R/W

—

VDDX

PUCR

Mode

Dep

Port E I/O pin, R/W in expanded modes

PE1

IRQ

—

VDDX

PUCR

Up

Port E input, external interrupt pin

PE0

XIRQ

—

VDDX

PUCR

Up

Port E input, non-maskable interrupt pin

PA[7:3]

ADDR[15:1/

DATA[15:1]

—

VDDX

PUCR

Disabled Port A I/O pin & multiplexed address/data

PA[2:1]

ADDR[10:9/

DATA[10:9]

—

VDDX

PUCR

Disabled Port A I/O pin & multiplexed address/data

PA[0]

ADDR[8]/

DATA[8]

—

VDDX

PUCR

Disabled

Port A I/O pin & multiplexed address/data

PB[7:5]

ADDR[7:5]/

DATA[7:5]

—

VDDX

PUCR

Disabled Port B I/O pin & multiplexed address/data

PB[4]

ADDR[4]/

DATA[4]

—

VDDX

PUCR

Disabled

Port B I/O pin & multiplexed address/data

PB[3:0]

ADDR[3:0]/

DATA[3:0]

—

VDDX

PUCR

Disabled Port B I/O pin & multiplexed address/data

PAD[7:0]

AN[7:0]

—

VDDA

PERAD/P

PSAD

Disabled

Port AD I/O pins and ATD inputs

PP[7]

KWP[7]

—

VDDX

PERP/

PPSP

Disabled Port P I/O Pins and keypad wake-up

PP[6]

KWP[6]

ROMCTL

VDDX

PERP/

PPSP

Disabled

Port P I/O Pins, keypad wake-up and ROMON

enable.

PP[5]

KWP[5]

PW5

VDDX

PERP/

PPSP

Disabled

Port P I/O Pin, keypad wake-up, PW5 output

PP[4:3]

KWP[4:3]

PW[4:3]

VDDX

PERP/

PPSP

Disabled Port P I/O Pin, keypad wake-up, PWM output