FUJITSU MB91401 User Manual

Page 66

MB91401

66

(10) I

2

C interface

•

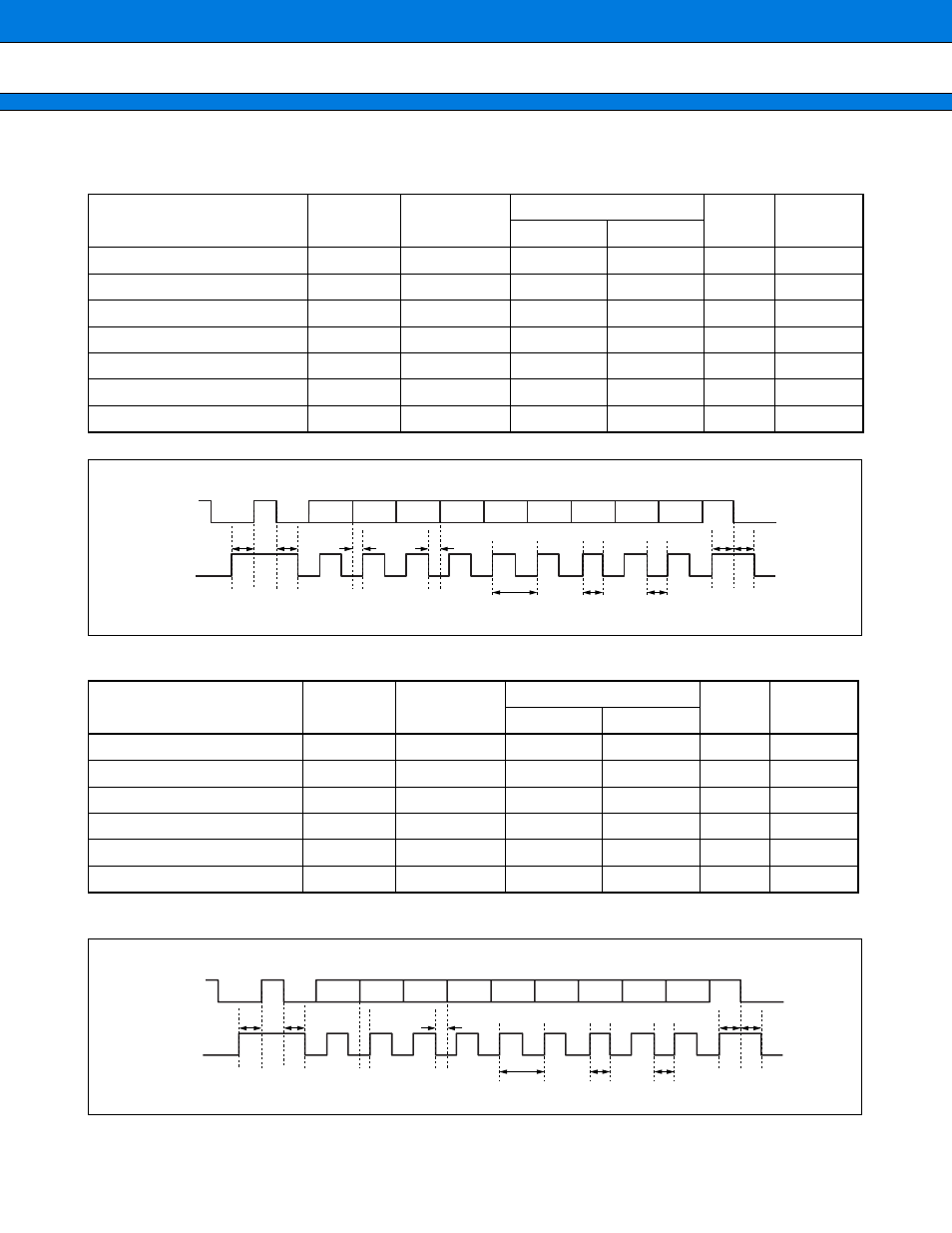

Input timing specification

* : Initial Value : I

2

C bus standards.

•

Output timing specification

* : For value m, refer to Section 7.5.2.3 “Clock Control Register (CCR) in the I

2

C Interface Specifications.” PCLK

indicates I

2

C interface operating clock frequency.

Parameter

Symbol

Pin

Value

Unit

Remarks

Min

Max

SDA input setup time

ts2sdai

SDA

250

ns

*

SDA input hold time

th2sdai

SDA

0

ns

*

SCL cycle time

tcscli

SCL

10

µ

s

*

SCL input “H” pulse time

twhscli

SCL

4

µ

s

*

SCL input “L” pulse time

twlscli

SCL

4.7

µ

s

*

SCL input setup time

ts2scli

SCL

4

µ

s

*

SCL input hold time

th2scli

SCL

4.7

µ

s

*

Parameter

Symbol

Pin

Value

Unit

Remarks

Min

Max

SCL output cycle time

tcsclo

SCL

(2

×

m)

+

2

PCLK

*

SCL output “H” Pulse Time

twhsclo

SCL

m

+

2

PCLK

*

SCL output “L” Pulse Time

twlsclo

SCL

m

PCLK

*

SCL output setup time

ts2sclo

SCL

m

+

2

PCLK

*

SCL output hold time

th2sclo

SCL

m

×

2

PCLK

*

SDA output hold time

th2sdao

SDA

5

PCLK

*

D7

D6

D5

D4

D3

D2

D1

D0 ACK

STOP

START

ts2scli

th2scli

ts2sdai

th2sdai

tcscli

twhscli

twlscli

ts2scli

th2scli

RESTART

SDA (input)

SCL (input)

D7

D6

D5

D4

D3

D2

D1

D0 ACK

STOP

START

ts2sclo

th2sclo

th2sdao

tcsclo

twhsclo

twlsclo

ts2sclo

th2sclo

RESTART

SDA (output)

SCL (output)

Prelminary

2004.11.12