FUJITSU MB91401 User Manual

Page 57

MB91401

57

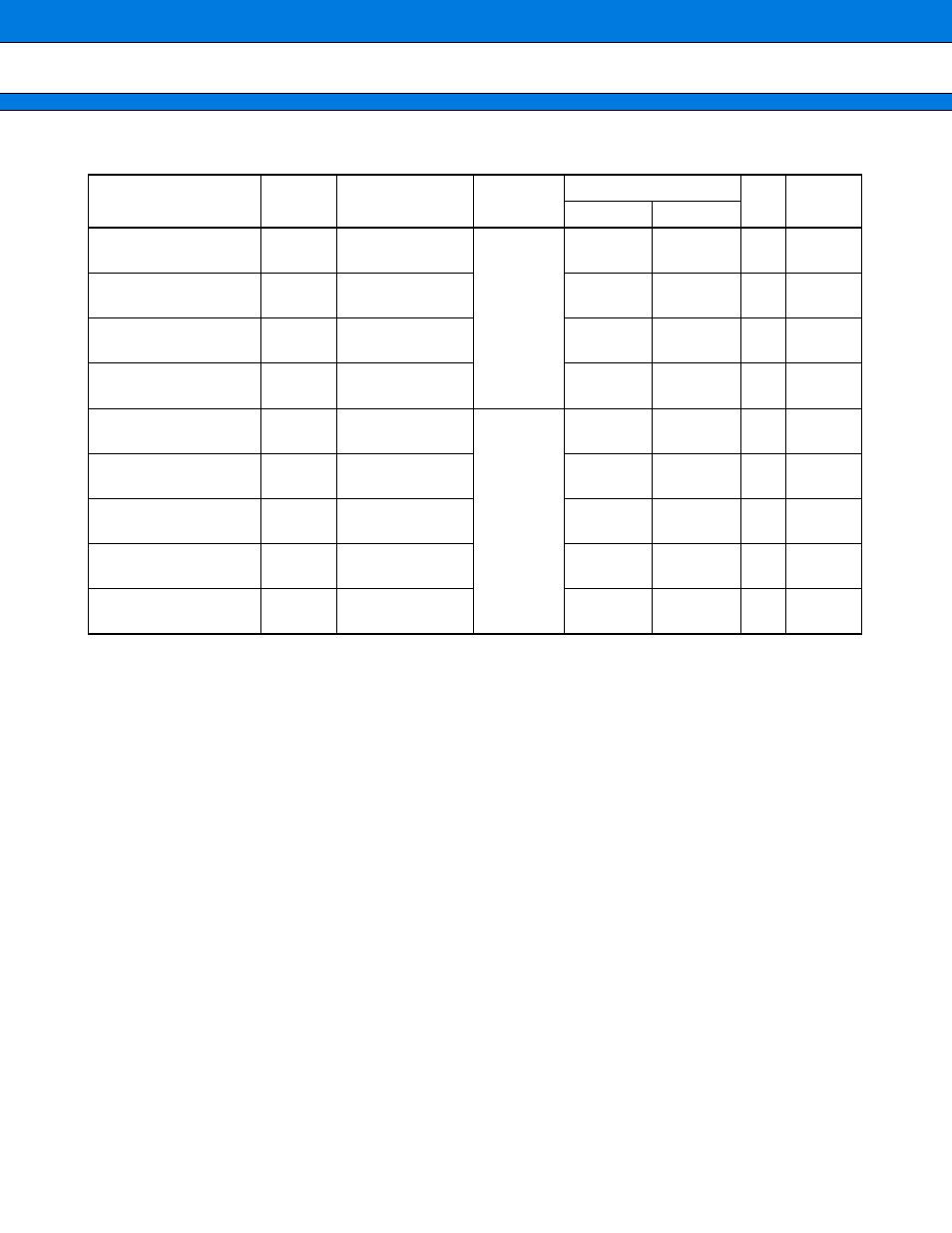

(5) UART

Note : timcycp is operational clock period of peripheral module built-in FR70E core.

Parameter

Symbol

Pin

Conditions

Value

Unit Remarks

Min

Max

Serial clock

cycle time

tscyc

SCK1, SCK0

Internal

shift clock

mode

8

×

timcycp

ns

SCLK

↓

→

SOUT delay time

tslov

SOUT1, SOUT0

−

80

80

ns

Valid SIN

→

SCLK

↑

tivsh

SIN1, SIN0

100

ns

SCLK

↑

→

valid SIN hold time

tshix

SIN1, SIN0

60

ns

Serial clock

“H” Pulse Width

tshsl

SCK1, SCK0

External

shift clock

mode

4

×

timcycp

ns

Serial clock

“L” Pulse Width

tslsh

SCK1, SCK0

4

×

timcycp

ns

SCLK

↓

→

SOUT delay time

tslov

SOUT1, SOUT0

150

ns

Valid SIN

→

SCLK

↑

tivsh

SIN1, SIN0

60

ns

SCLK

↑

→

valid SIN hold time

tshix

SIN1, SIN0

60

ns

Prelminary

2004.11.12