FUJITSU MB91401 User Manual

Page 46

MB91401

46

(Continued)

(2) NMI (Non Maskable Interrupt)

NMIs have the highest priority among the interrupt sources handled by this module.

An NMI is always selected whenever other types of interrupt sources occur at the same time.

• If an NMI occurs, the interrupt controller passes the information to the CPU :

Interrupt level : 15 (01111

B

)

Interrupt number : 15 (0001111

B

)

• NMI detection

NMIs are set and detected by the external interrupt/NMI controller. This module only generates an interrupt

level, interrupt number, and MHALTI upon NMI request.

• Suppressing DMA transfer upon NMI request

When an NMI request occurs, the MHALTI bit in the HRCL register is set to "1", suppressing DMA transfer. To

permit DMA transfer, clear the MHALTI bit to "0" at the end of the NMI routine.

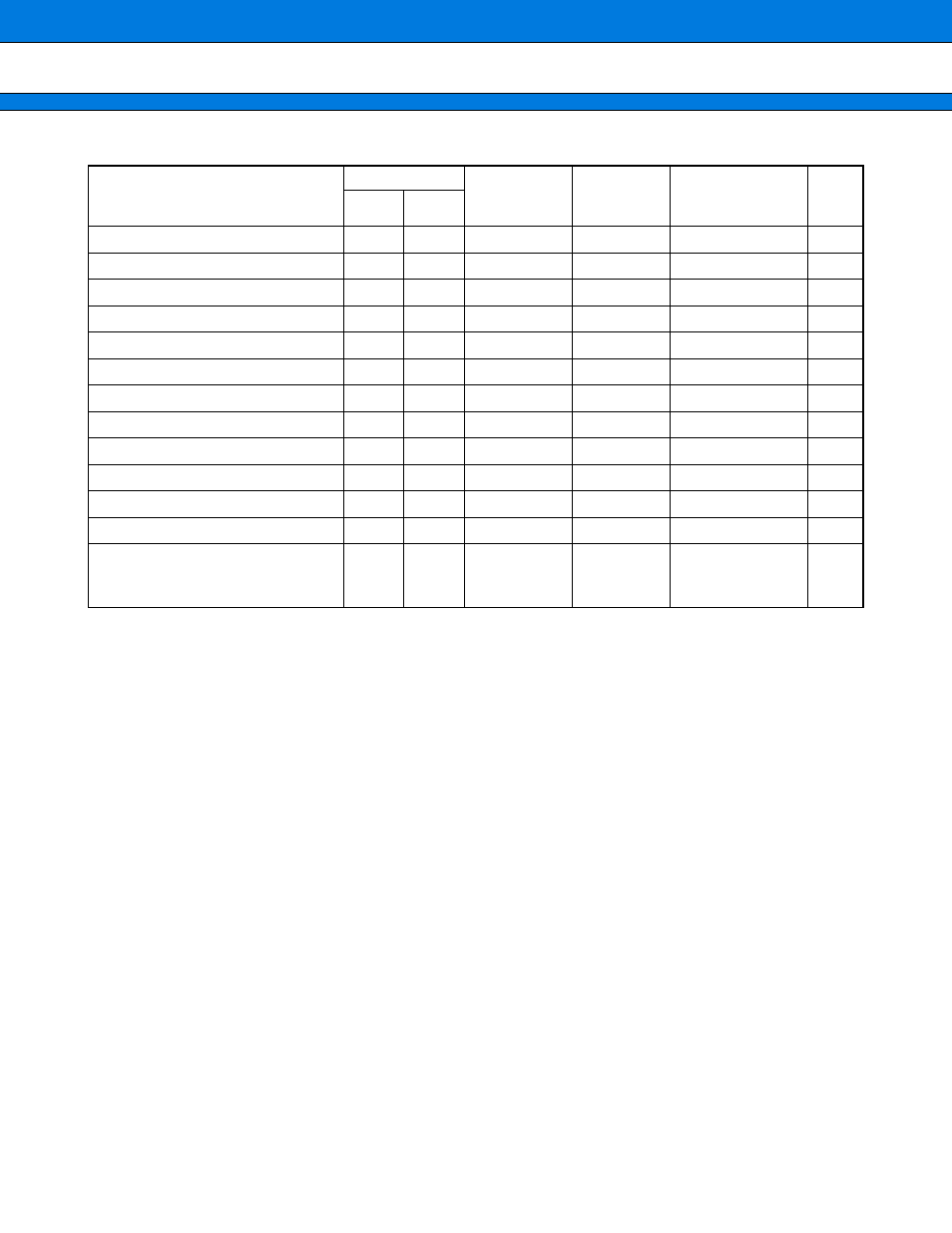

Interrupt source

Interrupt number

Interrupt

level

Offset

Address of TBR

default

RN

Decimal

Hexa-

decimal

System reserved

68

44

2EC

H

000FFEEC

H

System reserved

69

45

2E8

H

000FFEE8

H

System reserved

70

46

2E4

H

000FFEE4

H

System reserved

71

47

2E0

H

000FFEE0

H

System reserved

72

48

2DC

H

000FFEDC

H

System reserved

73

49

2D8

H

000FFED8

H

System reserved

74

4A

2D4

H

000FFED4

H

System reserved

75

4B

2D0

H

000FFED0

H

System reserved

76

4C

2CC

H

000FFECC

H

System reserved

77

4D

2C8

H

000FFEC8

H

System reserved

78

4E

2C4

H

000FFEC4

H

System reserved

79

4F

2C0

H

000FFEC0

H

Used by INT instruction

80

to

255

50

to

FF

2BC

H

to

000

H

000FFEBC

H

to

000FFC00

H

Prelminary

2004.11.12