I/o map – FUJITSU MB91401 User Manual

Page 34

MB91401

34

■

■

■

■

I/O MAP

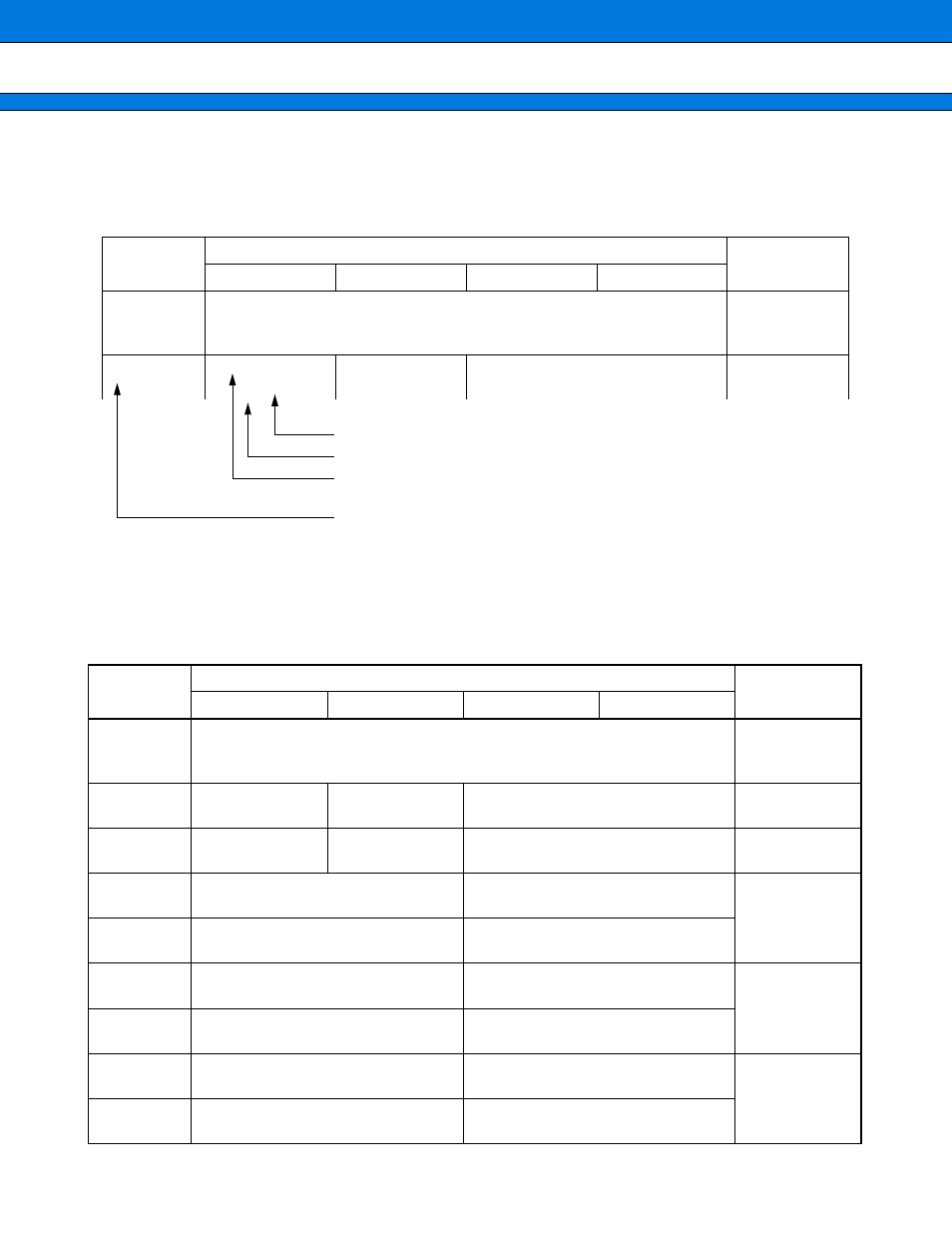

This shows the location of the various peripheral resource registers in the memory space.

[How to read the table]

Note : Initial values of register bits are represented as follows :

“1”

: Initial Value

“1”

“0”

: Initial Value

“0”

“X” : Initial Value

“X”

“-”

: Access prohibited in reserved area.

(Continued)

Address

Register

Block

++++

0

++++

1

++++

2

++++

3

0000_0000

H

to

0000_003C

H

Reserved

0000_0040

H

EIRR [R/W]

00000000

ENIR [R/W]

00000000

ELVR

00000000

[R/W]

00000000

Ext Int

0000_0044

H

DICR [R/W]

-------0

HRCL [R/W]

0-11111

DLYI/I-unit

0000_0048

H

TMRLR0

XXXXXXXX

[W]

XXXXXXXX

TMR0

XXXXXXXX

[R]

XXXXXXXX

Reload Timer 0

0000_004C

H

TMCSR0

----0000

[R/W]

00000000

0000_0050

H

TMRLR1

XXXXXXXX

[W]

XXXXXXXX

TMR1

XXXXXXXX

[R]

XXXXXXXX

Reload Timer 1

0000_0054

H

TMCSR1

----0000

[R/W]

00000000

0000_0058

H

TMRLR2

XXXXXXXX

[W]

XXXXXXXX

TMR2

XXXXXXXX

[R]

XXXXXXXX

Reload Timer 2

0000_005C

H

TMCSR2

----0000

[R/W]

00000000

Address

Register

Block

++++

0

++++

1

++++

2

++++

3

0000_0000

H

|

0000_003C

H

Reserved

0000_0040

H

EIRR [R/W]

00000000

ENIR [R/W]

00000000

ELVR [R/W]

00000000 00000000

Ext Int

Read/Write attribute

Initial value after a reset

Register name (First-column register at address 4n; second-column register

at address 4n + 2)

Left most register address (When accessing it by word, the register of

column 1 is positioned on the MSB side of data.)

Prelminary

2004.11.12