HP XU700 User Manual

Page 43

43

2 System Board

The Input/Output Controller Hub 2 (82801BA)

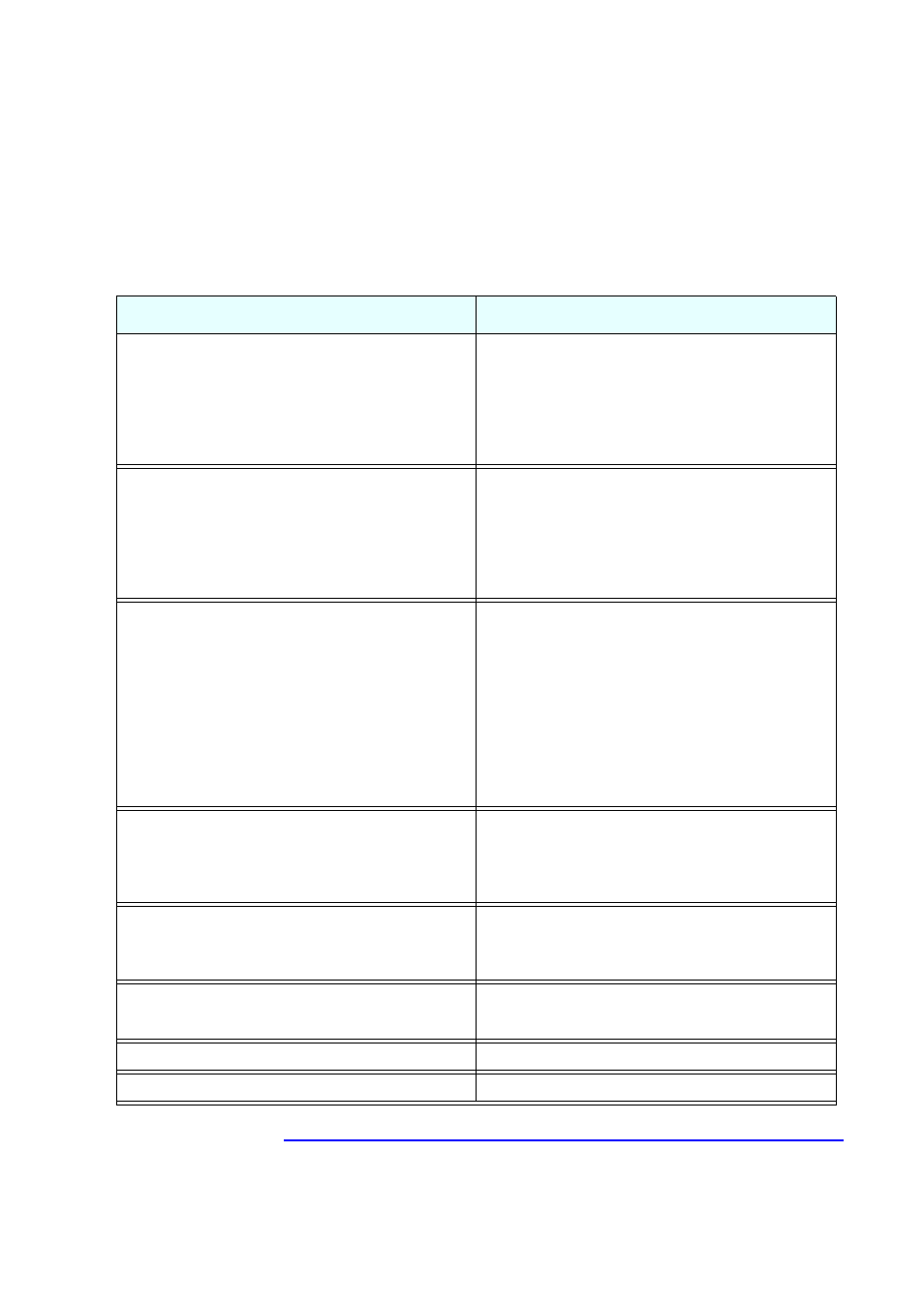

The following table shows the available ICH2 features.

Feature

Feature

• Multi-function PCI Bus Interface:

❒ PCI at 32-bit 33 MHz.

❒ PCI Rev 2.2 Specification.

❒ 133 Mbyte/sec data transfer rate.

❒ Master PCI Device Support for up to five devices.

• Enhanced DMA Controller:

❒ Two 82C37 DMA controllers.

❒ PCI DMA with 2 PC/PCI Channels in pairs.

❒ LPC DMA.

❒ DMA Collection Buffer to provide Type-F DMA performance

for all DMA channels.

• USB, supporting:

❒ USB revision 1.1 compliant.

❒ UHCI Implementation with four USB Ports for serial

transfers at12 or 1.5 Mbit/sec.

❒ Wake-up from sleeping states.

❒ Legacy keyboard/mouse software.

• Interrupt Controller:

❒ Two cascaded 82C59 controllers.

❒ Integrated I/O APIC capability.

❒ 15 Interrupt support in 8259 Mode, 24 supported in I/O APIC

mode.

❒ Serial Interrupt Protocol.

• Power Management Logic:

❒ ACPI 1.0 compliant.

❒ Support for APM-based legacy power management for non-

ACPI implementations.

❒ ACPI defined power states (S1, S3, S4, S5).

❒ ACPI power management timer.

❒ SMI generation.

❒ All registers readable/restorable for proper resume from 0 V

suspend states.

❒ PCI PME#.

• Integrated IDE Controller:

❒ Independent Timing of up to four drives.

❒ Ultra ATA/100 Mode (100 Mbytes/sec).

❒ Ultra ATA/66 Mode (66 Mbytes/sec).

❒ Ultra ATA/33 Mode (33 Mbytes/sec).

❒ PIO Mode 4 transfers up to 14 Mbytes/sec.

❒ Separate IDE connections for Primary and Secondary cables.

❒ Integrated 16 x 32-bit buffer for IDE PCI Burst transfers.

❒ Write Ping-Pong Buffer for faster write performances.

• Real-Time Clock, supporting:

❒ 256-byte battery-backed CMOS RAM.

❒ Hardware implementation to indicate Century Rollover.

• System TCO Reduction Circuits:

❒ Timers to Generate SMI# and Reset Upon.

❒ Timers to Detect Improper Processor Reset.

❒ Integrated Processor Frequency Strap Logic.

• Timers Based on 82C54:

❒ System Timer, Refresh Request, Speaker Tone Output.

• SMBus

❒ Host Interface allows processor to communicate via SMBus.

❒ Compatible with 2-wire I

2

C bus.

• System Timer, Refresh Request, Speaker Tone Output.

• GPIO:

❒ TTL, Open-Drain, Inversion.

• Firmware Hub (FWH) interface.

• 3.3 V operation with 5 V Tolerant Buffers for IDE and PCI signals.

• 241 BGA Package.

• Alert-On-LAN (AOL) support.