Avago Technologies ACPL-P347-000E User Manual

User manual

ACPL-P349, ACPL-W349

Isolated IGBT or SiC/GaN MOSFET Gate Driver Evaluation Board

User Manual

Quick-Start

This manual outlines the features of the ACPL-P349/W349 Evaluation Board and the configuration required for evaluat-

ing Isolated IGBT or SiC/GaN MOSFET Gate Drivers. Visual inspection is required to ensure that the evaluation board is

received in good condition.

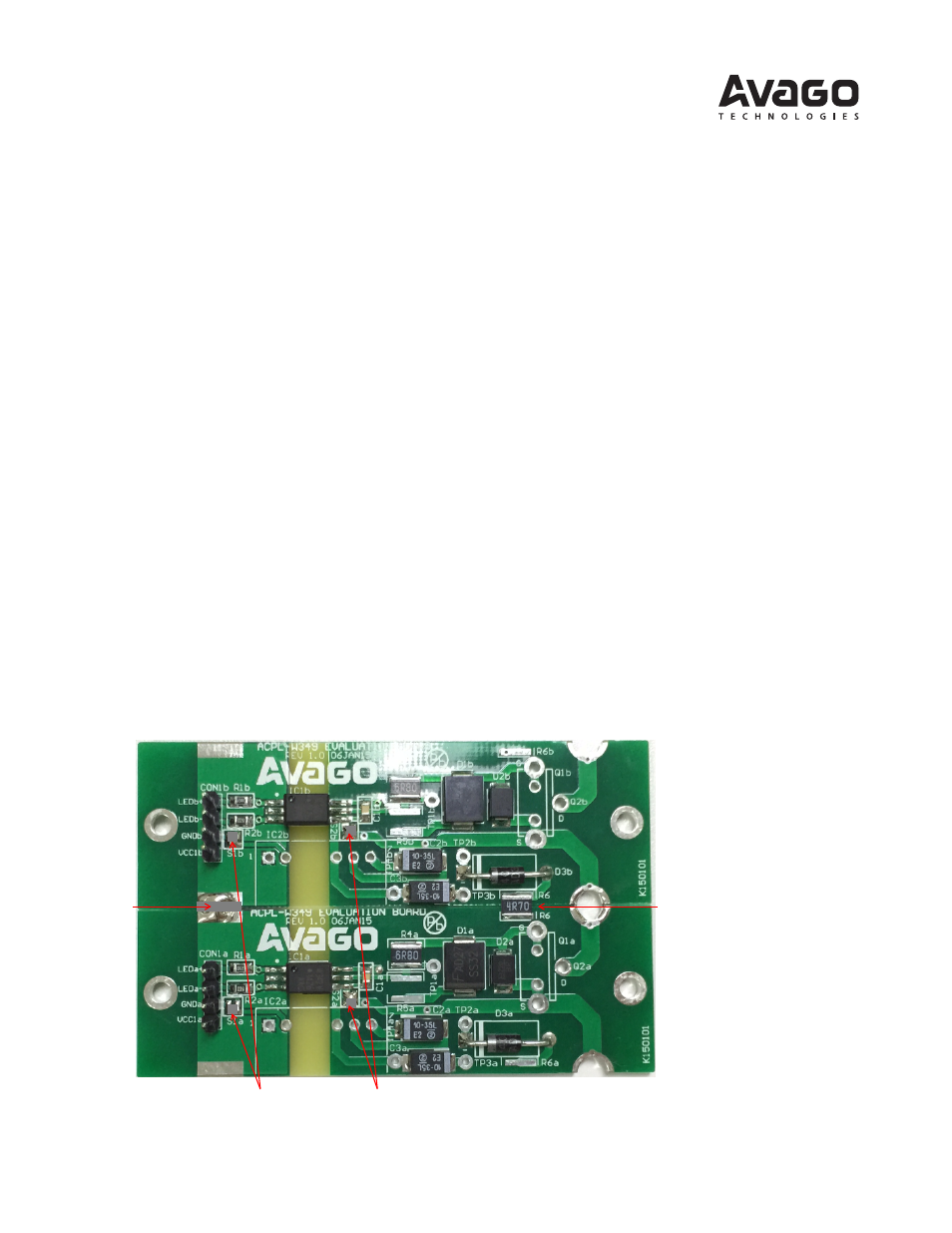

Default connections of the evaluation board are described below (refer to Figure 1):

1. Q1 and Q2 are not mounted. Either an IGBT or SiC/GaN MOSFET can be mounted at either Q1 (for TO-220 package)

or Q2 (for TO-247 package) or connected to the driver board through short wire connections from the holes provided

at Q1 or Q2;

2. D4 and R7 are not mounted (on solder side). A 15V zener footprint at D4 is provided to allow for a single DC power

supply of 15V~30V to be applied across Vcc2 and Vee if needed. A virtual ground Ve (at source pin of Q1 or Q2) can

then be generated and it acts as the reference point at the source pin of each SiC/GaN MOSFET (or emitter pin of each

IGBT). Vcc2 will then stay at 15V above the virtual ground Ve. R7 is needed to generate the bias current across D4;

3. S2 & S3 jumpers are shorted by default to connect Ve to Vee, assuming that a negative supply is not needed.

Note: If negative supply is needed, S2 & S3 jumpers need to be removed;

4. Bootstrap Diode D3b and Resistor R6 are connected by default. These 2 components are provided to help generate

Vcc2b supply through bootstrapping assuming that Vcc2a supply is available.

Note: Bootstrapping supply works only when Q1 or Q2 are mounted in a half bridge configuration and turned on and off

through proper PWM driving signals;

5. S1 is shorted by default to ground the IN- (or LED-, the cathode of LED) pin when Vcc1 is supplied. This short can be

removed if IN- cannot be grounded;

6. Upper and lower arms of the inverter will have common Vcc1 (& Gnd1), a provision is made to allow Vcc1 to be

connected by solder between upper and lower inverter PCB portions (and Gnd1 on the solder side);

7. Provisions are also made to allow Vcc2 (& Vee) to be generated from Vcc1 through a DC/DC converter at IC2. When

this DC/DC converter is used, S2, S3 (& R6) should be disconnected;

Figure 1. ACPL-P349/W349 Evaluation board showing default connections

Note: All part references are designated with suffix ‘a’ and ‘b’ to indicate lower and upper inverter arms respectively. If part references are made without

suffixes, then they are valid for both upper and lower inverter arms (except R6, which is shared).

S1(shorted)

S2(shorted)

S3 on solder side(also shorted)

Vcc1b

Vcc1a

Vcc1a & Vcc1b(shorted)

Gnda & Gndb on solder side(also shorted)

R6 mounted(soldered)