Avago Technologies LSI SAS 9205-8e User Manual

Page 6

LSISAS9205-8e PCI Express to 6Gb/s SAS HBA User Guide

May 2011

LSI Corporation

- 4 -

A scalable interface.

Serial, point-to-point interconnections between devices.

—

Reduces the electrical load of the connection

—

Enables higher transmission and reception frequencies

Lane reversal and polarity inversion.

PCIe hot plug.

Power management.

—

Supports PCI Power Management 1.2

—

Supports active-state power management (ASPM), including the L0 states, by placing links in a power-saving

mode when there is no link activity

A replay buffer that preserves a copy of the data for retransmission in case a cyclic redundancy check (CRC) error

occurs.

PCIe advanced error-reporting capabilities.

Packetized and layered architecture.

High bandwidth per pin with low overhead and low latency.

Software compatibility with PCI and PCI-X software.

—

Leverages existing PCI device drivers

—

Supports the memory, I/O, and configuration address spaces

—

Supports memory read/write transactions, I/O read/write transactions, and configuration read/write

transactions

Four kilobytes

of PCI configuration address space per device.

Posted transactions and non-posted transactions.

Quality-of-service (QOS) link configuration and arbitration policies.

Traffic Class 0 and

one virtual channel.

Message-signaled interrupts (both MSI and MSI-X), and INTx interrupt signaling for legacy PCI support.

End-to-end CRC (ECRC) and advanced error reporting.

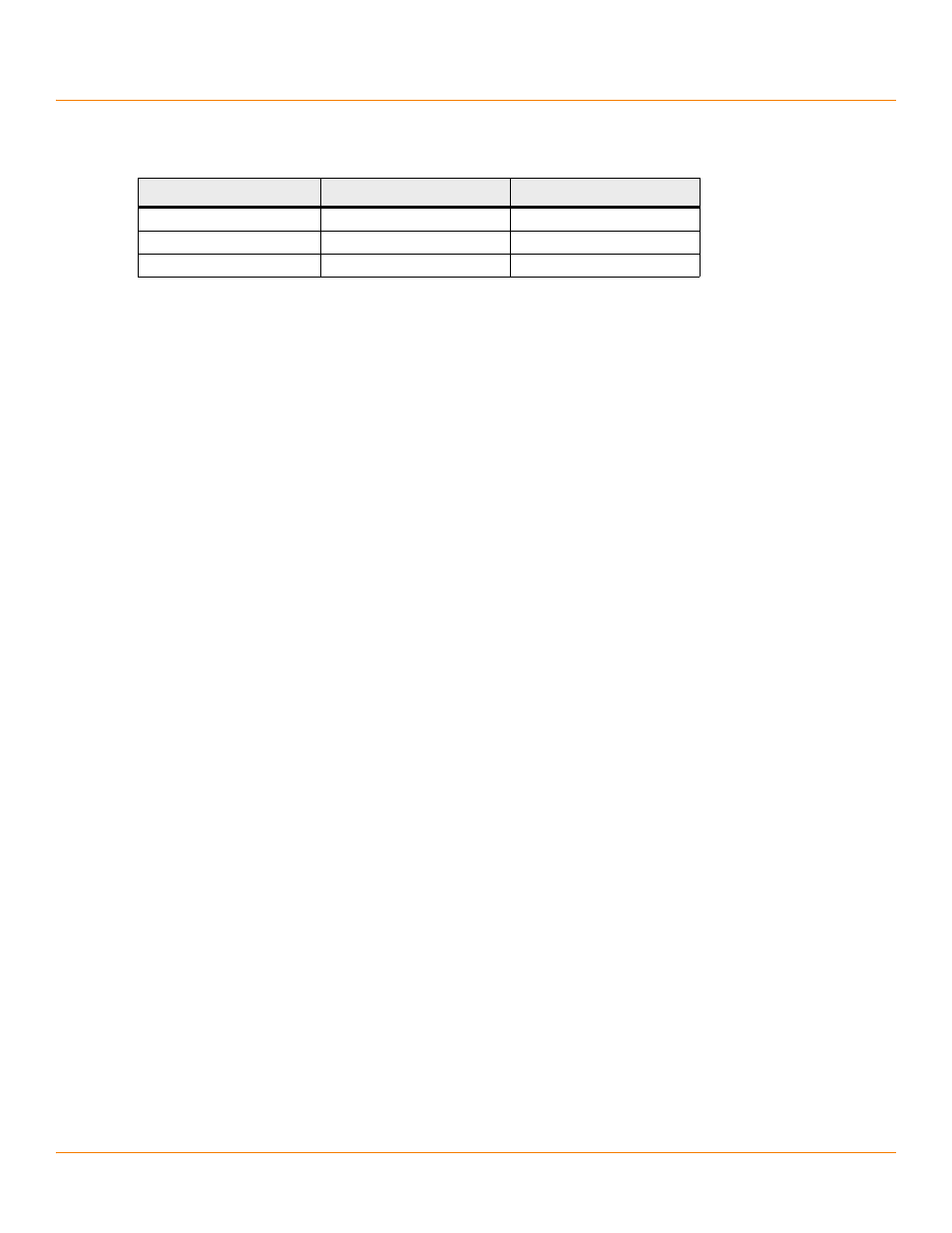

Table 2 Aggregate Bandwidth

Lanes

Single Direction

Dual Direction

Single-lane (x1)

5Gb/s

10Gb/s

Quad-lane (x4)

20Gb/s

40Gb/s

Eight-lane (x8)

40Gb/s

80Gb/s