Appendix, A. s1c6200a (advanced s1c6200) core cpu, A1 outline of differences – Epson S1C6200 User Manual

Page 90: A2 detailed description of the differences, Dvanced, A2.1 initial reset, A2.2 interrupt

84

EPSON

S1C6200/6200A CORE CPU MANUAL

APPENDIX A. S1C6200A (ADVANCED S1C6200) CORE CPU

APPENDIX

A. S1C6200A (A

DVANCED

S1C6200) C

ORE

CPU

S1C6200A is an improved version of the S1C6200. In this section, S1C6200A is described only in

terms of its differences with S1C6200. It is recommended that users of S1C6200A read this section.

S1C6200A is a Core CPU which has been made easier to integrate software by improving the parts of the

S1C6200 CPU which are difficult to use.

This section lists its differences with S1C6200; for items which are not included here, refer to the corre-

sponding section in this manual.

A1 Outline of Differences

• The D (decimal) flag is set to "0" during initial reset.

• Modifications of the interrupt circuit

- The interrupt timing has been shifted to 0.5 clock later.

-

and reading the interrupt factor flag during EI (enable interrupt flag) are possible. (However, consult

the respective hardware manuals to find out whether these are possible with the CPU peripheral

circuits.)

A2 Detailed Description of the Differences

A2.1 Initial reset

The D (decimal) flag will be set as follows through initial reset:

Table A2.1.1 D (decimal) flag initial setting

D (decimal) flag setting

S1C6200

Undefined

S1C6200A

0

CPU Core

Owing to this, bugs due to omission of D (decimal) flag setting during software development can now be

easily prevented.

For the values of other registers and flags during initial reset, see Section 2.5.4, "Initial reset".

A2.2 Interrupt

Operation during interrupt issuance

The time it takes to complete interrupt processing by hardware after the Core CPU receives the interrupt

request has changed as follows:

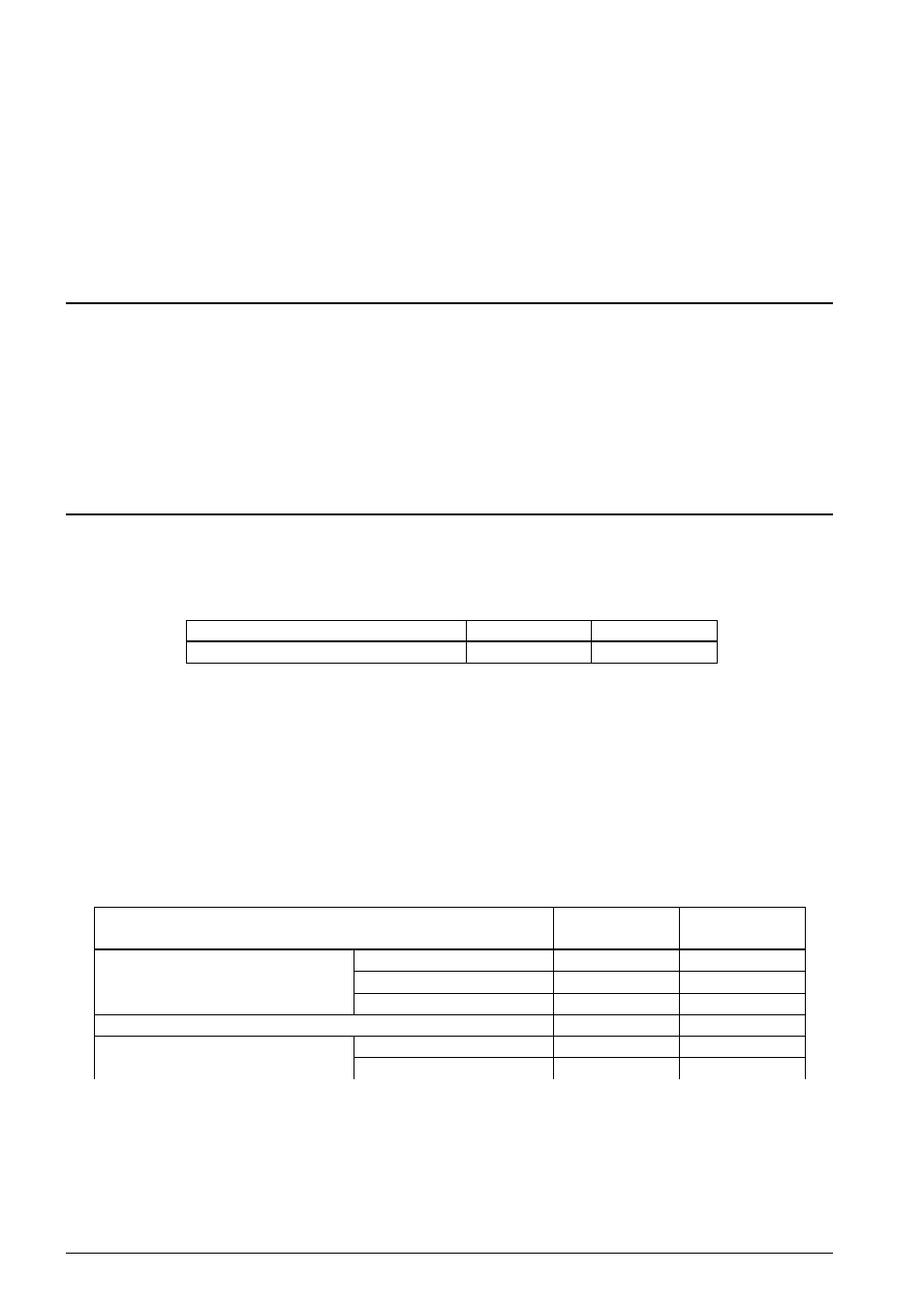

Table A2.2.1 Required interrupt processing time

a) During instruction execution

b) At HALT mode

c) During PSET instruction execution

S1C6200

(clock cycles)

13 to 25

13 to 20

13 to 18

14 to 15

13 to 25

13 to 23

S1C6200A

(clock cycles)

12.5 to 24.5

12.5 to 19.5

12.5 to 17.5

14 to 15

12.5 to 24.5

12.5 to 22.5

Item

12-cycle instruction execution

7-cycle instruction execution

5-cycle instruction execution

PSET + CALL

PSET + JP

Figure A2.2.1 shows the timing chart of the S1C6200A interrupt.