Epson S1C6200 User Manual

Page 27

S1C6200/6200A CORE CPU MANUAL

EPSON

21

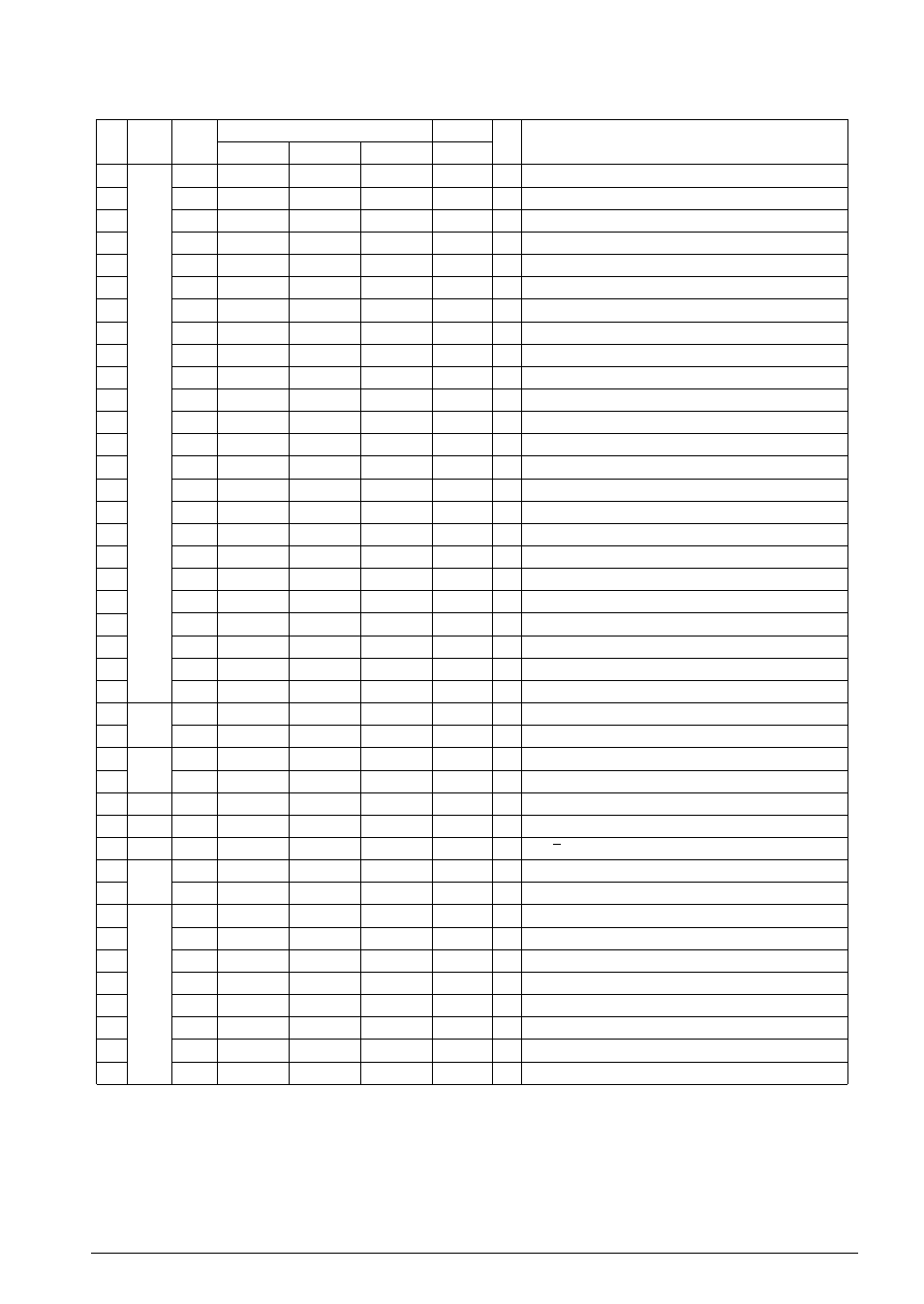

3 INSTRUCTION SET

B

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

A

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

1

1

1

0

1

1

1

1

1

1

1

1

0

1

1

1

1

1

1

1

1

9

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

1

1

1

1

1

1

0

0

1

1

1

1

1

1

1

1

1

8

1

1

1

1

0

0

1

1

0

0

0

0

0

0

1

1

0

0

0

1

0

0

0

0

0

0

0

0

1

1

1

0

0

1

1

1

1

1

1

1

1

7

1

1

1

1

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

e7

1

1

1

e7

0

1

0

1

1

1

0

1

1

1

1

1

1

1

1

1

1

6

0

0

0

0

0

1

1

1

0

0

0

0

0

0

1

1

0

0

0

e6

0

0

0

e6

1

1

1

1

1

1

0

1

1

1

1

1

1

1

1

1

1

5

1

1

0

0

r1

0

1

1

1

1

1

1

1

1

1

1

0

0

0

e5

0

0

0

e5

1

1

1

1

1

1

r1

r1

0

0

0

0

0

0

0

0

0

4

0

1

0

1

r0

0

0

1

0

0

0

1

1

1

0

1

0

0

0

e4

1

1

1

e4

0

0

1

1

1

1

r0

r0

1

1

1

1

1

1

1

1

1

3

n3

n3

n3

n3

i3

r1

0

0

0

1

0

0

1

0

0

0

0

1

0

e3

0

1

0

e3

i3

r1

i3

r1

1

1

1

i3

r1

1

0

0

0

0

1

1

0

2

n2

n2

n2

n2

i2

r0

1

1

1

0

0

1

0

0

0

0

1

0

0

e2

1

0

0

e2

i2

r0

i2

r0

0

1

1

i2

r0

0

0

1

1

1

0

0

1

1

n1

n1

n1

n1

i1

q1

r1

r1

r1

r1

r1

r1

r1

r1

r1

r1

r1

r1

r1

e1

r1

r1

r1

e1

i1

q1

i1

q1

1

1

1

i1

q1

1

r1

0

1

0

0

0

1

0

n0

n0

n0

n0

i0

q0

r0

r0

r0

r0

r0

r0

r0

r0

r0

r0

r0

r0

r0

e0

r0

r0

r0

e0

i0

q0

i0

q0

1

1

1

i0

q0

0

r0

1

0

0

0

1

1

A, Mn

B, Mn

Mn, A

Mn, B

r, i

r, q

r, SPH

r, SPL

r, XH

r, XL

r, XP

r, YH

r, YL

r, YP

SPH, r

SPL, r

XH, r

XL, r

XP, r

X, e

YH, r

YL, r

YP, r

Y, e

MX, i

r, q

MY, i

r, q

r

r, i

r, q

F

r

XH

XL

XP

YH

YL

YP

LD

LDPX

LDPY

NOP5

NOP7

NOT

OR

POP

I D Z C

↑

↑

↑

↑

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

7

7

7

7

5

5

5

5

5

5

5

5

A

←

M(n3~n0)

B

←

M(n3~n0)

M(n3~n0)

←

A

M(n3~n0)

←

B

r

←

i3~i0

r

←

q

r

←

SPH

r

←

SPL

r

←

XH

r

←

XL

r

←

XP

r

←

YH

r

←

YL

r

←

YP

SPH

←

r

SPL

←

r

XH

←

r

XL

←

r

XP

←

r

XH

←

e7~e4, XL

←

e3~e0

YH

←

r

YL

←

r

YP

←

r

YH

←

e7~e4, YL

←

e3~e0

M(X)

←

i3~i0, X

←

X+1

r

←

q, X

←

X+1

M(Y)

←

i3~i0, Y

←

Y+1

r

←

q, Y

←

Y+1

No operation (5 clock cycles)

No operation (7 clock cycles)

r

←

r

r

←

r

V

i3~i0

r

←

r

V

q

F

←

M(SP), SP

←

SP+1

r

←

M(SP), SP

←

SP+1

XH

←

M(SP), SP

←

SP+1

XL

←

M(SP), SP

←

SP+1

XP

←

M(SP), SP

←

SP+1

YH

←

M(SP), SP

←

SP+1

YL

←

M(SP), SP

←

SP+1

YP

←

M(SP), SP

←

SP+1

↓

↓

↓

↓

47

47

48

48

51

51

52

52

53

53

54

54

55

55

56

56

57

58

58

57

59

60

60

59

49

49

50

50

61

61

62

62

63

63

64

64

65

65

66

66

67

Page

Operand

Clock

Operation Code

Flag

Mne-

monic

Operation

↑↓

↑↓

↑↓