11 pinout – Sundance SMT166 User Manual

Page 37

11

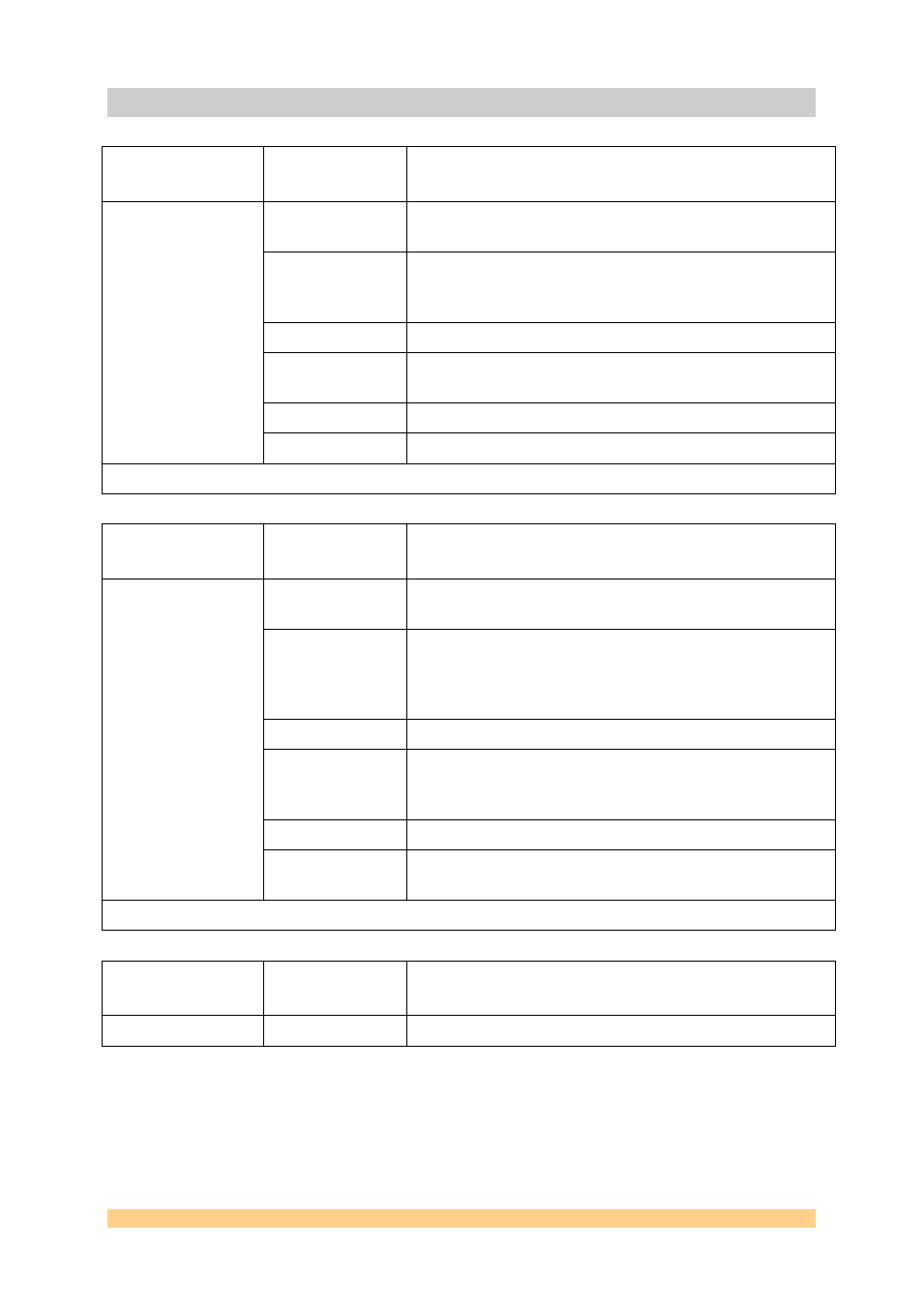

Pinout

Interface

Signal / Bus

FPGA Pin #

DDR3 Bank A

Addr[0:14]

M18 J19 K19 B17 C17 L18 L19 G17 H17 K17 K18

D17 E18 E17 F18

Data[0:31]

J16 A15 B15 G15 F15 H15 J15 D15 G13 H14 G11

F11 A13 A14 G12 H13 E14 H10 G10 K14 J14 M13

M11 C12 J12 A11 B11 J11 J10 D12 E12 K13

BA[0:2]

L15 H18 M17

Control

CS:J17 RAS:L14 CAS:B16 WE:F16 CKE:E16

ODT:D16 CKP:K16 CKN:L16 RESET:G16

DM[0:3]

C15 F14 H12 K12

DQSP/N[0:3]

M16/M15 D14/C14 B12/B13 E13/F13

All I/O are 1.5V with internal Vref. DCI cascade Master:35 Slave:36

Interface

Signal / Bus

FPGA Pin #

DDR3 Bank B

Addr[0:14]

AP16 AJ16 AJ17 AM15 AN15 AF16 AG16 AL14

AL15 AH15 AJ15 AJ14 AK14 AF15 A?G15

Data[0:31]

AE13 AE12 AJ11 AK11 AK12 AJ12 AF11 AE11

AL10 AG11 AG10 AJ10 AH10 AC12 AD11 AP12

AN12 AE14 AF14 AN13 AM13 AK13 AL13 AH13

AH19 AM17 AM16 AD17 AE17 AE18 AF18 AL16

BA[0:2]

AE16 AG17 AP15

Control

CS:AJ19 RAS:AD16 CAS:AC17 WE:AH18

CKE:AN17 ODT:AP17 CKP:AC15 CKN:AD15

RESET:AG18

DM[0:3]

AM10 AM12 AH14 AK16

DQSP/N[0:3]

AD14/AC14 AL11/AM11 AG12/AH12

AK18/AK17

All I/O are 1.5V with internal Vref. DCI cascade Master:33 Slave:32

Interface

Signal / Bus

FPGA Pin #

Flash

D[0:7]

AF24 AF25 W24 V24 H24 H25 P24 R24

Product Specification SMT166

Page 37 of 44

Last Edited: 17/06/2014 16:12:00