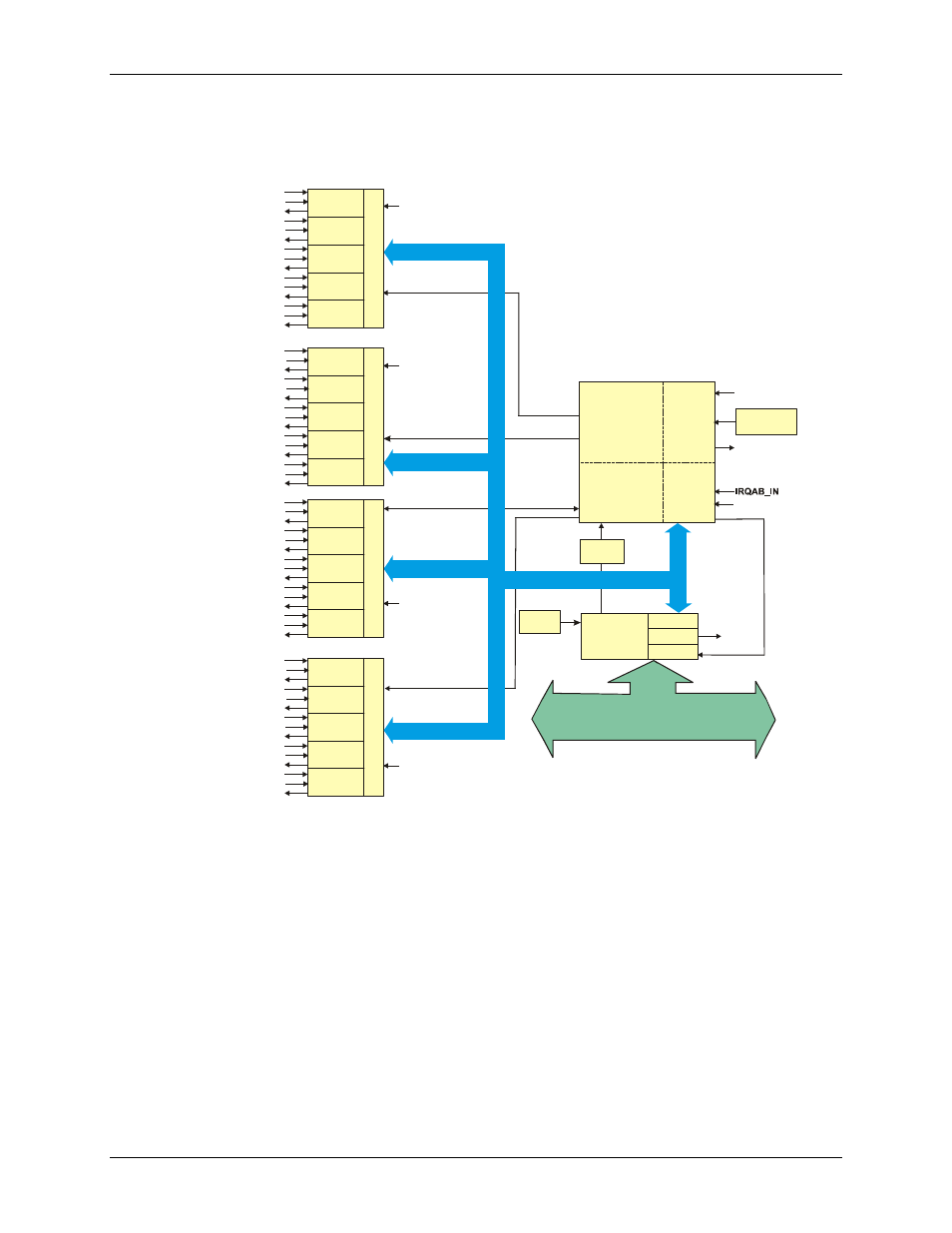

Pci-ctr20hd block diagram, Pci-ctr20hd block diagram -2, Figure 1-1. pci-ctr20hd functional block diagram – Measurement Computing PCI-CTR20HD User Manual

Page 8

PCI-CTR20HD User's Guide

Introducing the PCI-CTR20HD board

PCI-CTR20HD block diagram

PCI-CTR20HD functions are illustrated in the block diagram shown here.

PCI

Controller

BADR1

Interrupt

Boot

EEPROM

Control

Registers

Clock

Divider

Decode/Status

Int

Ctl

Bus

Timing

Clock Select

1/1.67/3.33/5 MHz

Controller FPGA and Logic

PCI BUS (5V/3.3V, 32-BIT, 33 MHZ)

Clock

Select

BADR2

Counter A

CTS9513

16-Bit Counters

1/1.67/3.33/5 MHz

or

EXT SRCA_IN

IRQCD_IN

LOCAL BUS

Co

nt

r

o

l

Counter 1

Counter 2

Counter 3

Counter 4

Counter 5

Counter 1

Con

trol

Counter 2

Counter 3

Counter 4

Counter 5

Co

n

t

ro

l

Counter 1

Counter 2

Counter 3

Counter 4

Counter 5

Counter 1

C

ontr

o

l

Counter 2

Counter 3

Counter 4

Counter 5

CTR1CLK_A

CTR1GATE_A

CTR1OUT_A

Co

n

tr

o

l

Contr

o

l

CONTROL

BUS

CONTROL

BUS

CONTROL

BUS

CONTROL

BUS

CTR2CLK_A

CTR2GATE_A

CTR2OUT_A

CTR3CLK_A

CTR3GATE_A

CTR3OUT_A

CTR4CLK_A

CTR4GATE_A

CTR4OUT_A

CTR5CLK_A

CTR5GATE_A

CTR5OUT_A

CTR1CLK_B

CTR1GATE_B

CTR1OUT_B

CTR2CLK_B

CTR2GATE_B

CTR2OUT_B

CTR3CLK_B

CTR3GATE_B

CTR3OUT_B

CTR4CLK_B

CTR4GATE_B

CTR4OUT_B

CTR5CLK_B

CTR5GATE_B

CTR5OUT_B

CTR1CLK_C

CTR1GATE_C

CTR1OUT_C

CTR2CLK_C

CTR2GATE_C

CTR2OUT_C

CTR3CLK_C

CTR3GATE_C

CTR3OUT_C

CTR4CLK_C

CTR4GATE_C

CTR4OUT_C

CTR5CLK_C

CTR5GATE_C

CTR5OUT_C

CTR1CLK_D

CTR1GATE_D

CTR1OUT_D

CTR2CLK_D

CTR2GATE_D

CTR2OUT_D

CTR3CLK_D

CTR3GATE_D

CTR3OUT_D

CTR4CLK_D

CTR4GATE_D

CTR4OUT_D

CTR5CLK_D

CTR5GATE_D

CTR5OUT_D

Counter B

CTS9513

16-Bit Counters

Counter C

CTS9513

16-Bit Counters

Counter D

CTS9513

16-Bit Counters

1/1.67/3.33/5 MHz

or

EXT SRCB_IN

1/1.67/3.33/5 MHz

or

EXT SRCC_IN

1/1.67/3.33/5 MHz

or

EXT SRCD_IN

10 MHz

Oscillator

Figure 1-1. PCI-CTR20HD functional block diagram

1-2