Measurement Computing CIO-DAS-TEMP User Manual

Page 16

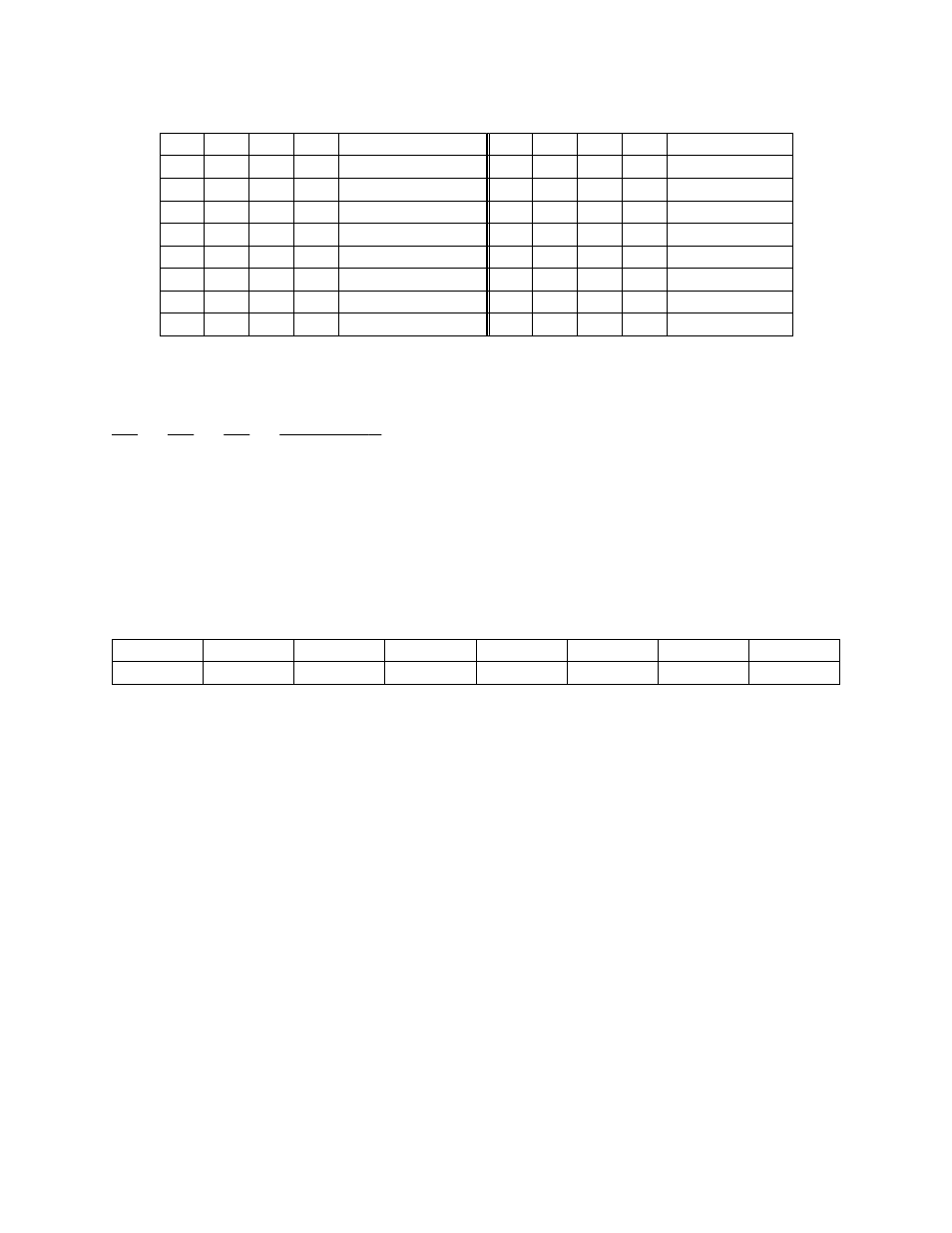

Table 5-2. Prescalar Divider/2 MHz Clock Control Codes

61.01

1

1

1

1

15,625

1

1

1

0

122.07

0

1

1

1

31,250

0

1

1

0

244.14

1

0

1

1

62,500

1

0

1

0

488.28

0

0

1

1

125,000

0

0

1

0

976.56

1

1

0

1

250,000

1

1

0

0

1,953

0

1

0

1

500,000

0

1

0

0

3,906.25

1

0

0

1

None

1

0

0

0

7,812.5

0

0

0

1

None

0

0

0

0

Output Freq

P0

P1

P2

P3

Output Freq

P0

P1

P2

P3

When TMRE = 0, the Prescaler and Counter 2 are disabled. When TMRE = 1, the prescaler and Counter

2 are enabled.

IR2

IR1

IR0

Hardware IRQ

0

0

0

Disable interrupts

0

0

1

Disable interrupts

0

1

0

2

0

1

1

3

1

0

0

4

1

0

1

5

1

1

0

6

1

1

1

7

BASE + 5 Read - Read bit settings

IR0

IR1

IR2

TMRE

P0

P1

P2

P3

0

1

2

3

4

5

6

7

BASE + 6 Write - Load counter 0

A write to this address loads the v alue 65,535 into counter 0. T his must be done before trig gering a

conversion.

BASE + 7 Not used

12

See also other documents in the category Measurement Computing Hardware:

- ACC-300 (7 pages)

- AI-EXP32 (20 pages)

- AI-EXP48 (19 pages)

- BTH-1208LS (30 pages)

- 6K-ERB08 (32 pages)

- BTH-1208LS Quick Start (4 pages)

- 6K-SSR-RACK08 (33 pages)

- BTH-1208LS-OEM (27 pages)

- CB-COM-Digital (68 pages)

- CB-7018 (68 pages)

- CB-7000 Utilities (44 pages)

- CB-7080D (74 pages)

- CB-COM-7033 (44 pages)

- CB-COM-7017 (72 pages)

- CB-COM-7024 (76 pages)

- CB-NAP-7000P (36 pages)

- CIO-DAC02/16 (16 pages)

- CIO-DAC02 (18 pages)

- CB-NAP-7000D (56 pages)

- CIO-DAC16-I (16 pages)

- CIO-DAC16/16 (20 pages)

- CIO-DAS08 (21 pages)

- CIO-DAC16 (20 pages)

- CIO-DAS08/JR (16 pages)

- CIO-DAS08/JR/16 (14 pages)

- CIO-DAS08/JR-AO (16 pages)

- CIO-DAS08-AOM (32 pages)

- CIO-DAS08-PGM (28 pages)

- CIO-DAS16/330 (34 pages)

- CIO-DAS48-I (17 pages)

- CIO-DAS16/M1 (38 pages)

- CIO-DAS48-PGA (18 pages)

- CIO-DAS800 (20 pages)

- CIO-DAS802/16 (22 pages)

- CIO-DAS6402/16 (40 pages)

- CIO-DDA06/16 (18 pages)

- CIO-DDA06/JR (17 pages)

- CIO-DIO24/CTR3 (21 pages)

- CIO-DIO24H (20 pages)

- CIO-DI192 (24 pages)

- CIO-DDA06 (21 pages)

- CIO-DIO48 (19 pages)

- CIO-DO192H (16 pages)

- CIO-DIO192 (20 pages)