Measurement Computing CIO-DAS-TEMP User Manual

Page 15

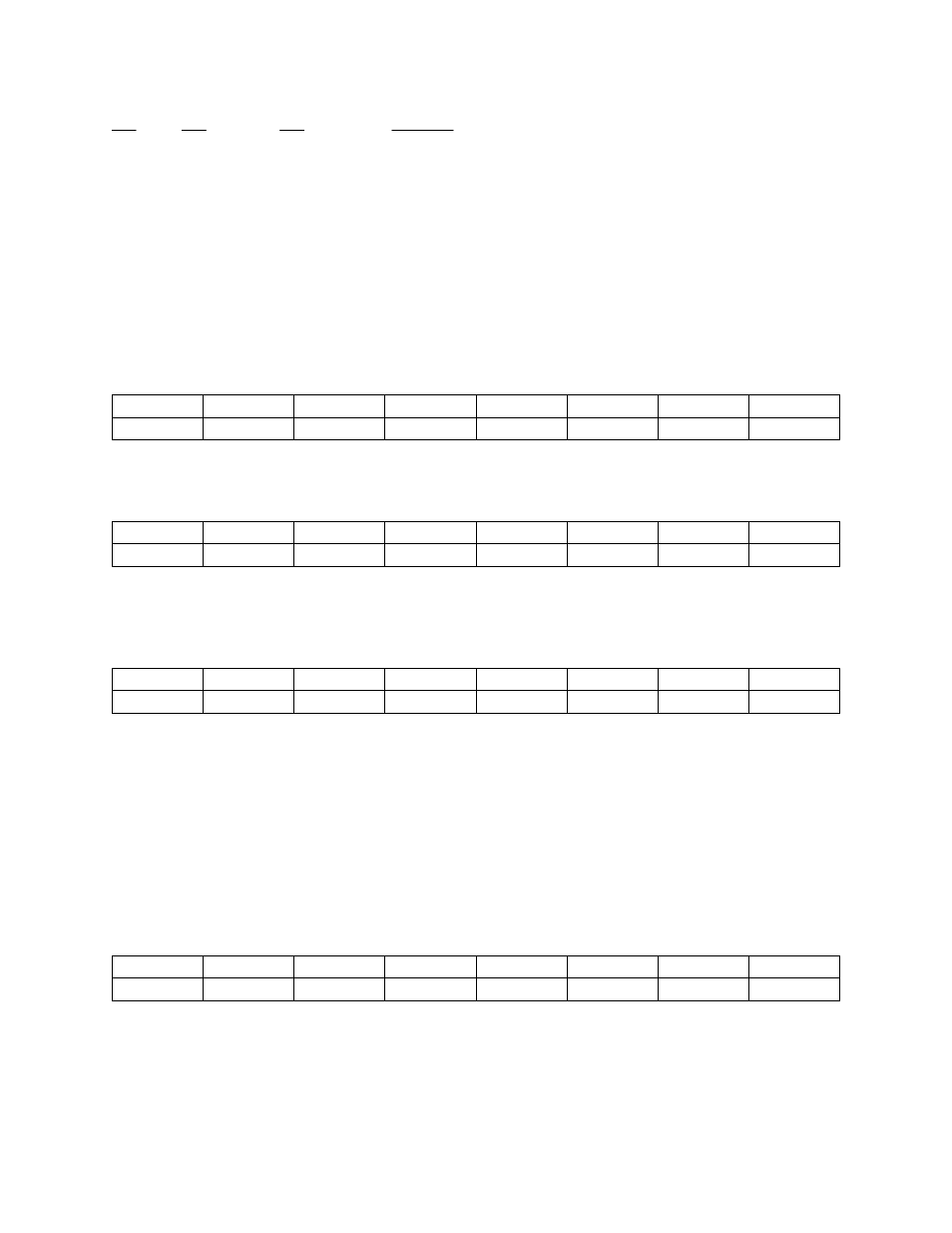

M1

M0

M0

Function

0

0

0

Program selected counter as event counter, mode 0

0

0

1

Hardware triggered one shot. Pulse is the duration of

the load value

0

1

0

Rate generator. CLK is divided by load value

0

1

1

Square wave. Period equals CLK divided by load value

1

0

0

Software triggered strobe

1

0

1

Hardware triggered strobe

When BCD = 0, the counter counts in binary, 16-bit count. When BCD = 1, the counter counts in

binary-coded-decimal.

BASE + 3 Read - Status Register of the 82C54

BCD

M0

M1

M2

RW0

RW1

SC0

SC1

0

1

2

3

4

5

6

7

Will return current status.

BASE + 4 Write - Channel select and mux enable

CH0

CH1

CH2

CH3

CH4

X

X

CHEN

0

1

2

3

4

5

6

7

Select channel 0 to 31 in standard binary counting. CHEN enables the mux so that the current channel

sensor is connected to the output of the mux

BASE + 4 Read - Channel, interrupt, calibration switch and EOC status

CH0

CH1

CH2

CH3

CH4

CONV

CAL

INT

0

1

2

3

4

5

6

7

CH4 through CH0 read back the current channel.

CONV is high when a conversion is in progress and low when conversion is complete, that is when the

counter value in counter 1 has reached zero.

CAL indicates the position of the CAL/NORM switch. NORM = 0, CAL = 1

INT is the status of the interrupt flip flop. It is set whenever conversion is complete (terminal count in

counter 1) whether or not interrupts are enabled. Clear INT by reading Base + 5.

BASE + 5 Write - Interrupt select and trigger mode

IR0

IR1

IR2

TMRE

P0

P1

P2

P3

0

1

2

3

4

5

6

7

P3 through P0 control a prescalar divider or a 2MHz clock by 4 to 32768 in the steps shown in Table 5-2

below. The output of the prescaler is the input to counter 2, the channel mux sequencer.

11