Register map, Control registers, 6 register map – Measurement Computing CIO-DAS-TEMP User Manual

Page 13: 1 control registers

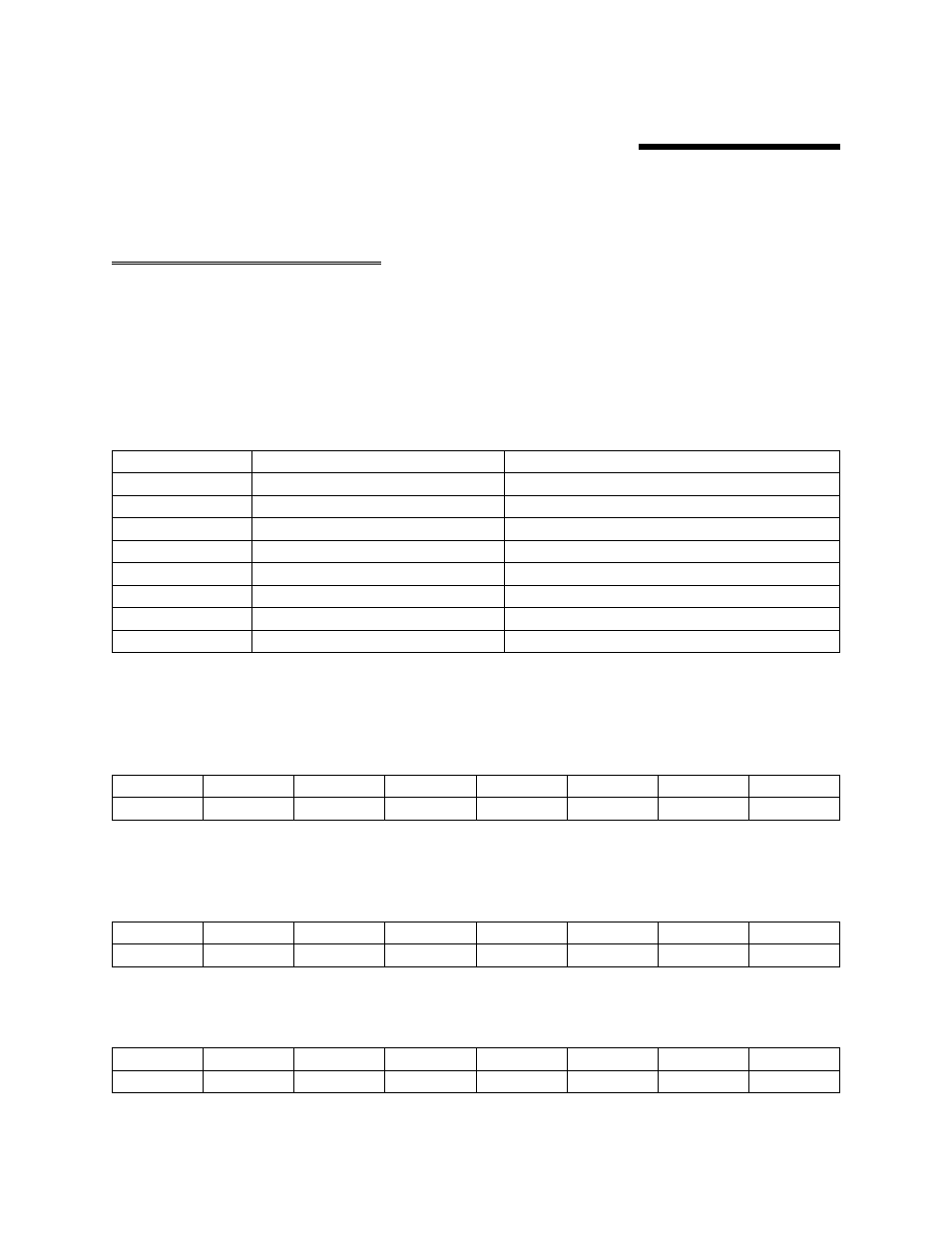

6 REGISTER MAP

A base address register controls the beg inning, or 'Base Address' of the I /O addresses occupied by the

control registers of the CIO-DAS-TEMP. In all, eight addresses are occupied. The registers control the

programmable aspects of the CIO-DAS-TEMP performance.

6.1 CONTROL REGISTERS

After a base address has been established, the CIO-DAS-TEMP is controlled by writing to and reading

from the control registers. While it is possible to w rite your own control routines for the

CIO-DAS-TEMP, routines have been written and are available in Universal Library for DOS and

Windows programming languages. Unless you have a specific need to program at the register level, it is

recommended that you use the Universal Library or a packaged application program.

Table 5-1. Control Registers

Counter Control

None

BASE + 7

Reload

None

BASE + 6

Clear

Interrupt & Prescaler Control

BASE + 5

Channel Control & Status

Channel & Status

BASE + 4

8254 Counter Control

8254 Status

BASE + 3

Data Load

8254 Counter 2 Data Read

BASE + 2

Data Load

8254 Counter 1 Data Read

BASE + 1

Data Load

8254 Counter 0 Data Read

BASE + 0

WRITE

READ

I/O ADDRESS

Register Descriptions

The register descriptions include functions of each bit in each 8-bit register as well as some design and

use descriptions

BASE + 0 Write - Counter 0 Load Register of the 82C54

Data 0

Data 1

Data 2

Data 3

Data 4

Data 5

Data 6

Data 7

0

1

2

3

4

5

6

7

Write an initial value of 65,536 to this reg ister after programming the 82C54 control register for CTR 0

to be an event counter. It works as a down-counter, the only choice available.

BASE + 0 Read - Counter 0 Current Count Register of the 82C54

Data 0

Data 1

Data 2

Data 3

Data 4

Data 5

Data 6

Data 7

0

1

2

3

4

5

6

7

The total of the V/F output should be read from this register after Counter 1 reaches terminal count

BASE + 1 Write - Counter 1 Load Register of the 82C54

Data 0

Data 1

Data 2

Data 3

Data 4

Data 5

Data 6

Data 7

0

1

2

3

4

5

6

7

9