4 register architecture – Measurement Computing CIO-DAC16-I User Manual

Page 11

4 REGISTER ARCHITECTURE

The CIO-DAC##-I is a simple board to understand. All control and data is

read/written with simple I/O read and write commands. No interrupt or DMA

control software is required. Thus, the board's outputs are easy to control directly

from BASIC, C or PASCAL.

The CIO-DAC##-I has two control and analog output registers.

The first address, or BASE ADDRESS, is determined by the setting of a bank of

switches on the board.

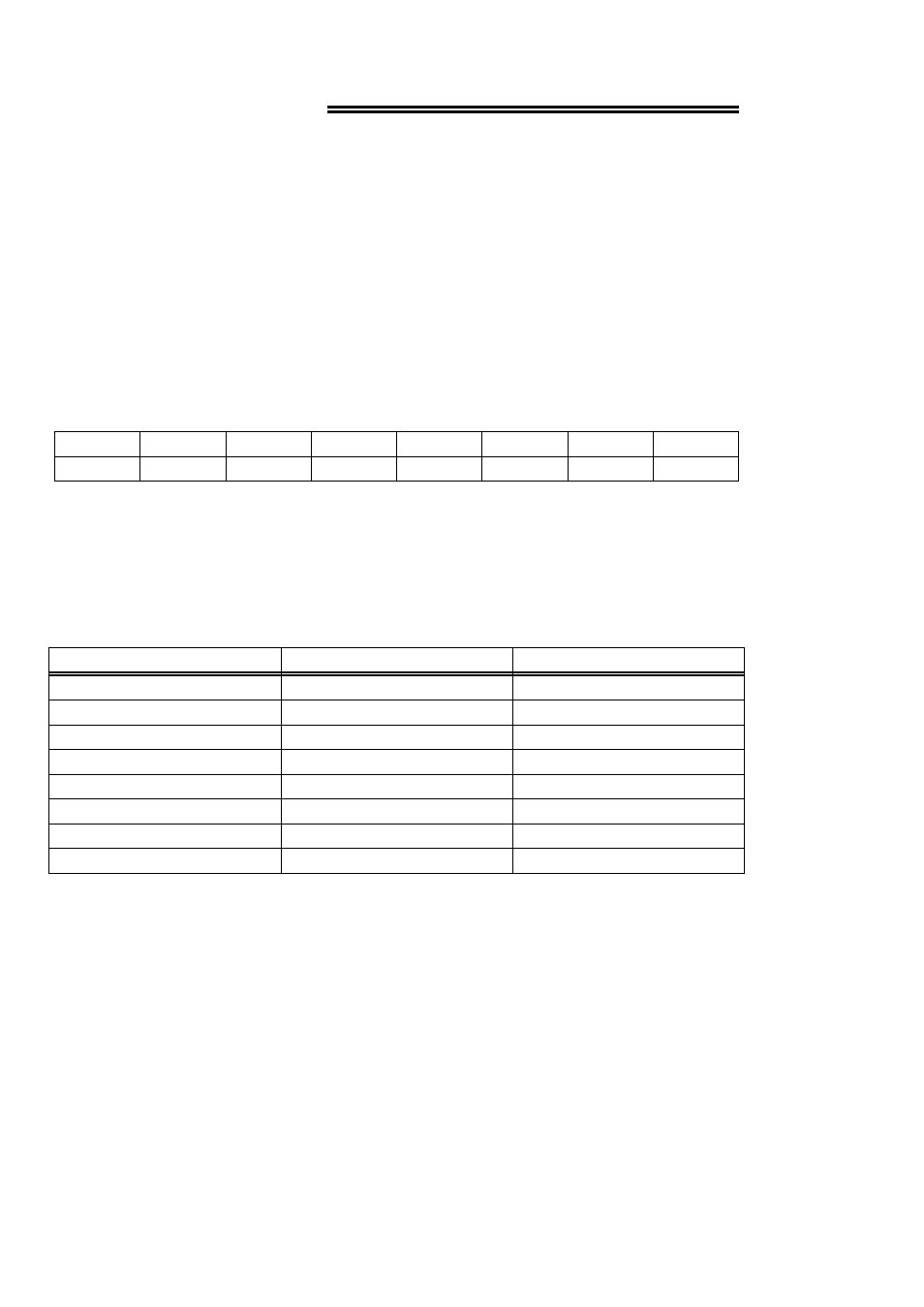

The register descriptions all follow the format:

A0

A1

A2

A3

A4

A5

A6

A7

0

1

2

3

4

5

6

7

the numbers along the top row are the bit positions within the 8-bit byte and the

numbers and symbols in the bottom row are the functions associated with each bit.

To write to or read from a register in decimal or HEX, the following weights apply:

Table 4-1. Register Bit Weights

80

128

7

40

64

6

20

32

5

10

16

4

8

8

3

4

4

2

2

2

1

1

1

0

HEX VALUE

DECIMAL VALUE

BIT POSITION

7

- ACC-300 (7 pages)

- AI-EXP32 (20 pages)

- AI-EXP48 (19 pages)

- BTH-1208LS (30 pages)

- 6K-ERB08 (32 pages)

- BTH-1208LS Quick Start (4 pages)

- 6K-SSR-RACK08 (33 pages)

- BTH-1208LS-OEM (27 pages)

- CB-COM-Digital (68 pages)

- CB-7018 (68 pages)

- CB-7000 Utilities (44 pages)

- CB-7080D (74 pages)

- CB-COM-7033 (44 pages)

- CB-COM-7017 (72 pages)

- CB-COM-7024 (76 pages)

- CB-NAP-7000P (36 pages)

- CIO-DAC02/16 (16 pages)

- CIO-DAC02 (18 pages)

- CB-NAP-7000D (56 pages)

- CIO-DAC16/16 (20 pages)

- CIO-DAS08 (21 pages)

- CIO-DAC16 (20 pages)

- CIO-DAS08/JR (16 pages)

- CIO-DAS08/JR/16 (14 pages)

- CIO-DAS08/JR-AO (16 pages)

- CIO-DAS08-AOM (32 pages)

- CIO-DAS08-PGM (28 pages)

- CIO-DAS16/330 (34 pages)

- CIO-DAS48-I (17 pages)

- CIO-DAS16/M1 (38 pages)

- CIO-DAS48-PGA (18 pages)

- CIO-DAS800 (20 pages)

- CIO-DAS802/16 (22 pages)

- CIO-DAS6402/16 (40 pages)

- CIO-DAS-TEMP (20 pages)

- CIO-DDA06/16 (18 pages)

- CIO-DDA06/JR (17 pages)

- CIO-DIO24H (20 pages)

- CIO-DIO24/CTR3 (21 pages)

- CIO-DI192 (24 pages)

- CIO-DDA06 (21 pages)

- CIO-DIO48 (19 pages)

- CIO-DO192H (16 pages)

- CIO-DIO192 (20 pages)