Filtered dac outputs configuration – Delta Tau PMAC2A-PC/104 User Manual

Page 30

PMAC2A PC104 Hardware Reference Manual

Software Setup

24

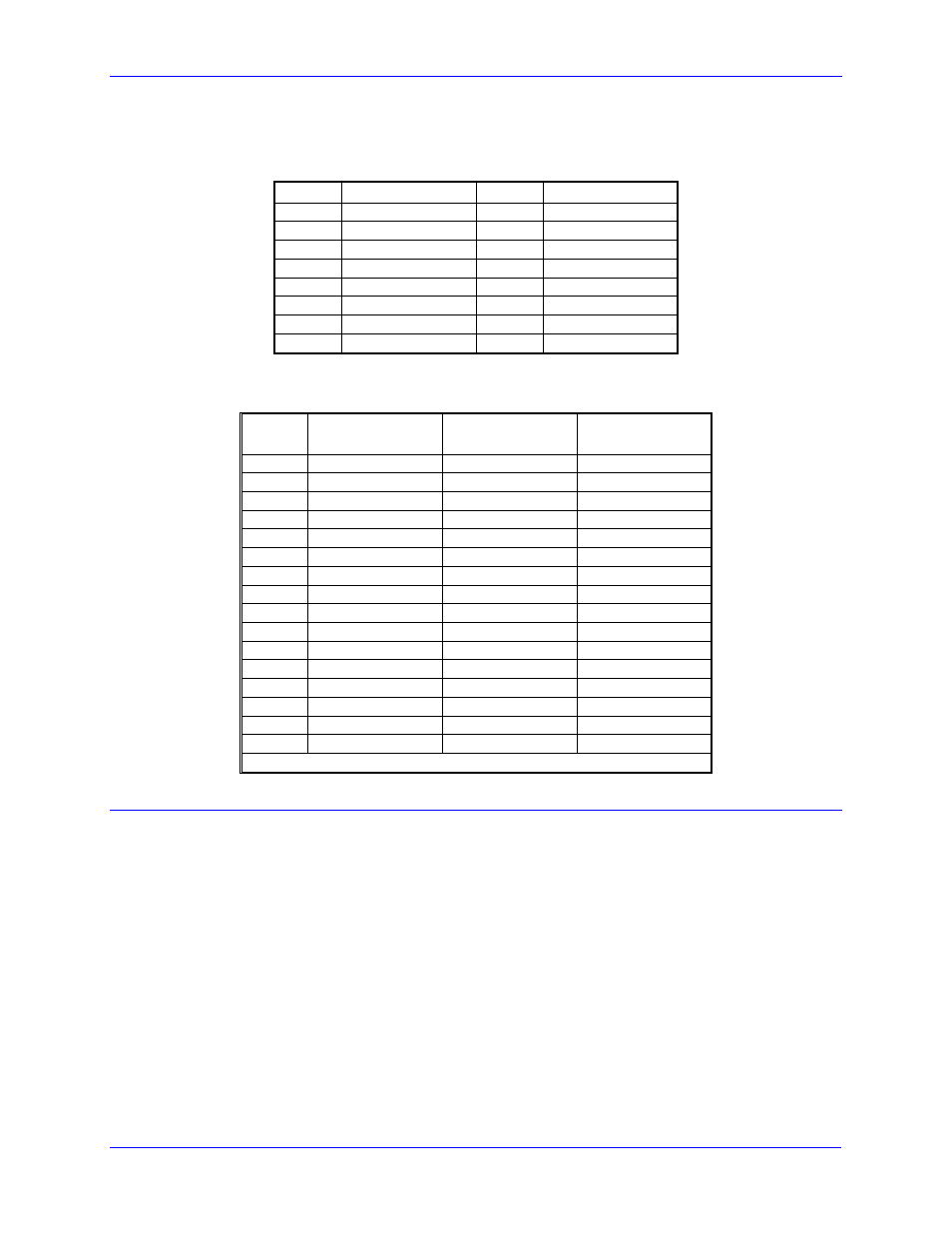

If the CPU’s operational frequency has been determined by (a non-zero setting of) I46, the serial

communications baud rate is determined at power-up/reset by variable I54 alone according to the

following table:

I54

Baud Rate

I54

Baud Rate

0 600 8 9600

1 900 9

14,400

2 1200 10

19,200

3 1800 11

28,800

4 2400 12

38,400

5 3600 13

57,600

6 4800 14

76,800

7 7200 15

115,200

For a saved value of 0 for I46, the serial baud rate is determined by the combination of I54 and the CPU

frequency as shown in the following table.

I54

Baud Rate for

40 MHz CPU

Baud Rate for

60 MHz CPU

Baud Rate for

80 MHz CPU

0 600 Disabled 1200

1 900*

(-0.05%)

900

1800*

(-0.1%)

2

1200 1200 2400

3

1800* (-0.1%)

1800

3600* (-0.19%)

4

2400 2400 4800

5

3600*

(-0.19%) 3600 7200*

(-0.38%)

6

4800 4800 9600

7 7200*

(-0.38%)

7200

14,400*(-0.75%)

8 9600

9600

19,200

9 14,400*(-0.75%)

14,400

28,800*(-1.5%)

10

19,200 19,200 38,400

11 28,800*(-1.5%)

28,800

57,600*(-3.0%)

12

38,400 38,400 76,800

13 57,600*(-3.0%)

57,600

115,200*(-6.0%)

14 76,800

76,800

153,600

15

Disabled 115,200 Disabled

* Not an exact baud rate

Filtered DAC Outputs Configuration

The following I-variables must be set properly to use the digital-to-analog (filtered DAC) outputs:

I900 =

1001

; PWM frequency 29.4kHz, PWM 1-4

I901 =

2

; Phase Clock 19.6kHz

I902 =

3

; Servo frequency 4.9kHz

I903 =

1746

; ADC frequency

I906 =

1001

; PWM frequency 29.4kHz, PWM 5-8

I907 =

1746

; ADC frequency

I9n6 =

0

; Output mode: PWM

Ix69 =

1001

; DAC limit 10Vdc

I10 =

1710933

; Servo interrupt time

n = channel number from 1 to 8

x = motor number from 1 to 8