Register communication kl6051 – BECKHOFF KL6051 User Manual

Page 11

Register description

KL6051

11

R15: alignment bits (RAM)

With the alignment bits, the analog terminal is set to a byte limit in the ter-

minal bus.

HB = LB converted (contains zero in the event of input)

LB = number of bit doublets 0,1,2,3

Manufacturer parameter

R16: hardware version [R/W]

HB = main number X of X.y

LB = sub-number y of X.y

User parameters

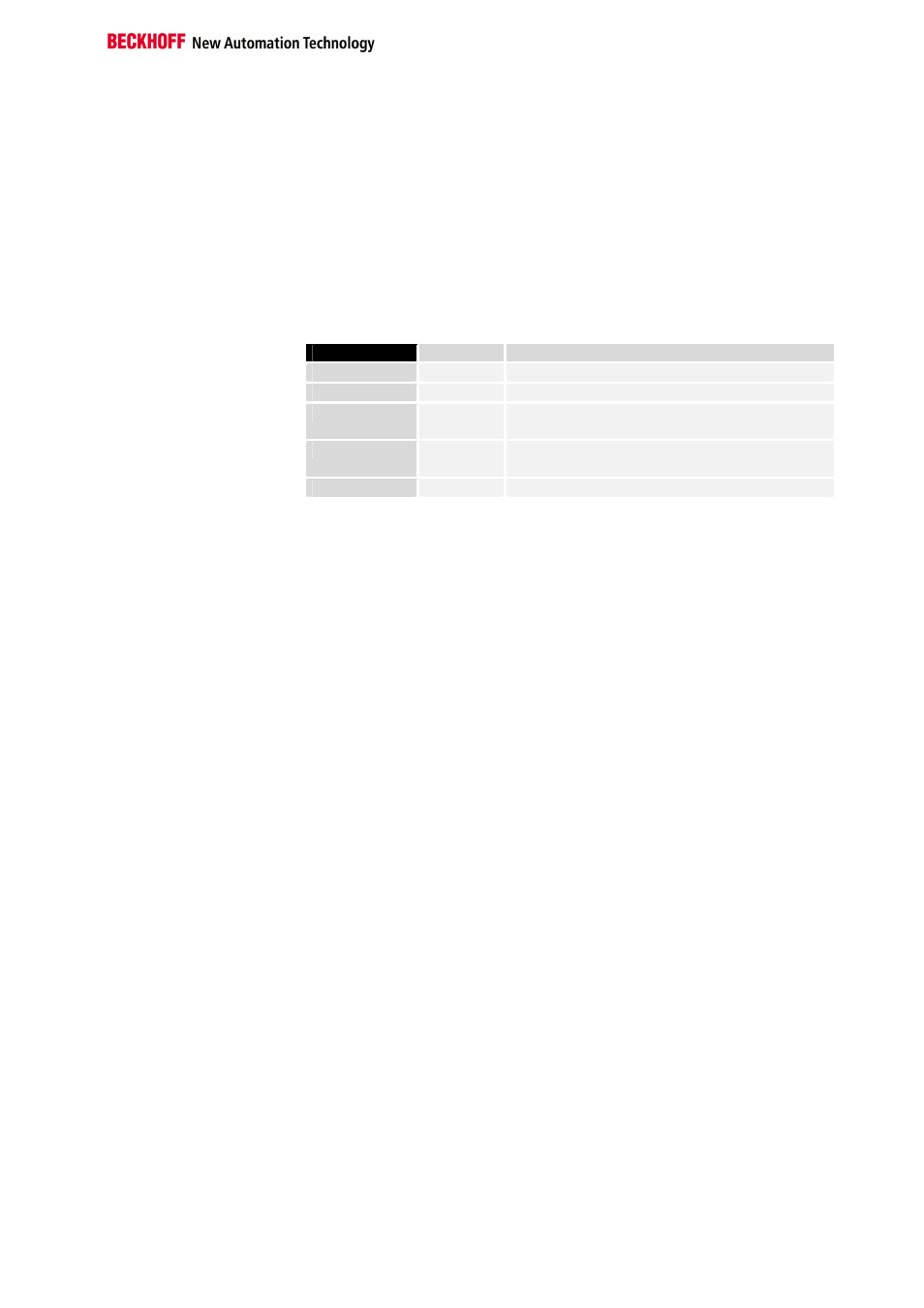

R32 Feature register

[0x0007]

Feature bit nr.

bit 0

1

RCV-timeout enable (R334) [1]

bit 1

1

TRS-timeout enable (R35) [1]

bit 2

0/1

0: terminal bus communiction via interrupt

1: terminal bus: poll state [1]

bit 3

0/1

0: data is transferred word-consistently

1: data is transferred completely consistently

bit 15-4

-

not used

R33: Baud rate

[0x0003] (62.5kHz)

HB = DC

LB = Baud rate = 4MHz / (16 * (LB + 1))

R34: RCV timeout

[0x00014] (200ms)

HB, LB = unsigned integer, 1 digit corresponds to 10ms

When the RCV timeout enable bit is set in R32, this value is valid. If the

terminal does not receive any valid data via the serial interface for X-ms,

the controller's inputs are set to the value ZERO.

R35: TRS timeout

[0x0014] (200ms)

HB, LB = unsigned integer,1 digit corresponds to 10ms

When the TRS timeout enable bit is set in R32, this value is valid. If the

terminal does not receive any valid data via the serial interface for X-ms,

no data is sent via the serial interface. Accordingly, the RCV timeout of the

2rd terminal would take effect.

Register communication KL6051

Register access via

process data transfer

Bit 7=1: register mode

When bit 7 of the control byte is set, the first two bytes of the user data are

not used for process data transfer, but are written into or read out of the

terminal’s register.

Bit 6=0: read

Bit 6=1: write

In bit 6 of the control byte, you define whether a register is to be read or

written. When bit 6 is not set, a register is read without modification. The

value can be taken from the input process image.

When bit 6 is set, the user data is written into a register. The operation is

concluded as soon as the status byte in the input process image has supp-

lied an acknowledgement (see examples).

Bits 0 to 5: address

The address of the register to be addressed is entered in bits 0 to 5 of the

control byte.