AMETEK CW Series Programming Manual User Manual

Page 19

Status Register Definitions

Elgar CW-P Series

A-2

Programming Manual

Bit 2, Error/Event Queue Information Available

This bit is set when any error/event is entered in the System Error queue. It is

read using the SYSTem:ERRor? query.

Bit 4, Message Available

Indicates a message is available in the GPIB output queue. This bit is cleared

after the GPIB output buffer is read.

Bit 5, Standard Event Status Register

This is a summary bit for the ESR. It is set when any of the ESR bits are set,

and cleared when the ESR is read.

Bit 6, Request Service/Master Summary Status

If service requests are enabled (with the *SRE command), this bit represents the

RQS and will be sent in response to a serial poll, then cleared. If RQS is not

enabled, the bit represents the MSS bit and indicates the device has at least one

reason to request service. Although the device sends the MSS bit in response to

a status query (*STB?), it is not sent in response to a serial poll. It is not

considered part of the IEEE 488.1 Status Byte.

A.2 Standard Event Status Register

The ESR can be read by the *ESR? command. Reading this register, or using the

*CLS command will clear the ESR.

Bits in the ESR will be set only when the corresponding bit in the Standard Events

Status Enable register is set. Use the *ESE to set bits, and the *ESE? to read this

register. To configure the CW-P Series to generate SRQ's based on the ESR, both the

Standard Event Status Enable register and the Service Request Enable registers must

be programmed.

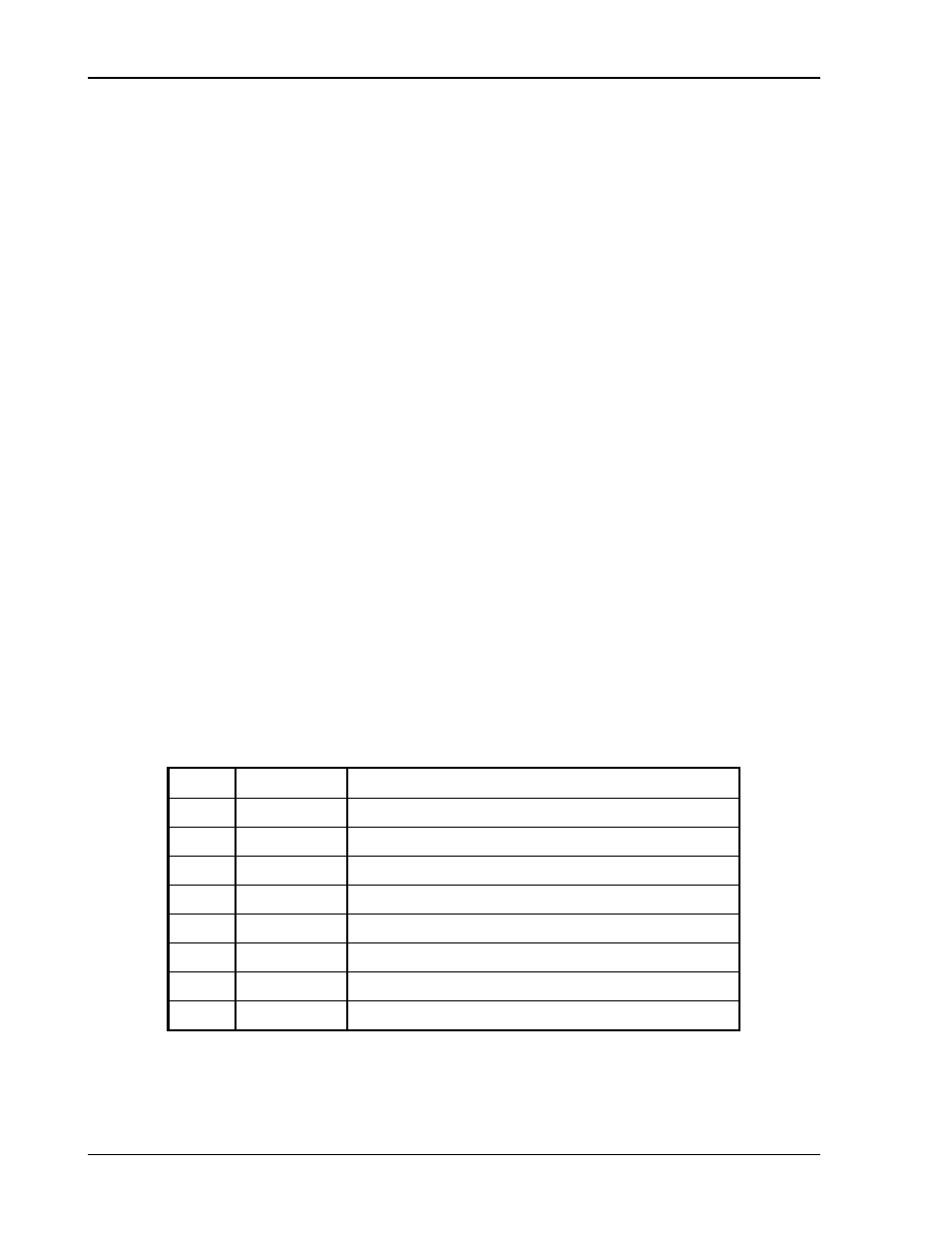

Bit

Hex Value Description

0

01

Operation Complete.

1

02

Request Control - Not used.

2

04

Query Error.

3

08

Device-Dependent Error.

4

10

Execution Error (e.g., range error).

5

20

Command Error (e.g., syntax error).

6

40

User Request - Not used.

7

80

Power On.