NEXCOM NEX 716VL2G User Manual

Page 68

67

Appendix A

NEX716VL2G User Manual

The NEX716VL 2G s eries features a wat chdog timer t hat res et the CPU or generates an interrupt if the

processor stops operating for any reason. This feature ensures system reliability in industrial standalone or

unmanned environments.

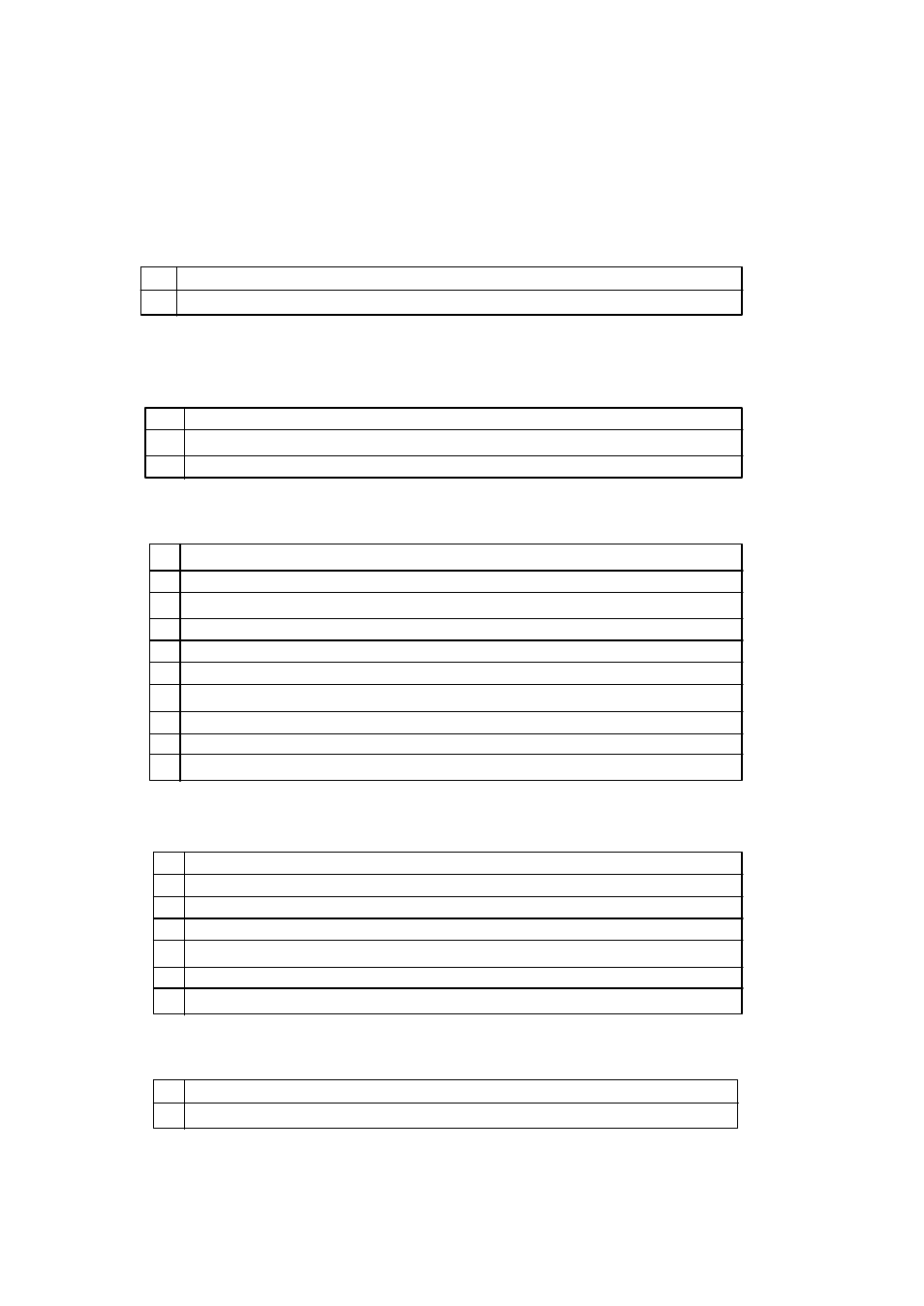

Panel Button De-bounce Base Address LSB Register (Index=65h, Default=00h)

Bit Description

7-0 Read/write, mapped as Base Address[7:0]

Panel Button De-bounce Interrupt Level Select Register (Index=70h, Default=00h)

Bit Description

7-4 Reserved

3-0 Select the interrupt level (note1) for Panel Button De-bounce

Watch Dog Timer Control Register (Index=71h, Default=00h)

Bit Description

7 WDT is reset upon a CIR interrupt.

6 WDT is reset upon a KBC (mouse) interrupt.

5 WDT is reset upon a KBC (keyboard) interrupt.

4 WDT is reset upon a read or a write to the Game Port base address.

3-2 Reserved

1 Force Time-out. This bit is self-clearing.

WDT Status

0 1:WDT value reaches 0.

0:WDT value is not 0.

Watch Dog Timer Configuration Register (Index=72h, Default=00h)

Bit Description

WDT Time-out value select

7 1:Second

0:Minute

6 WDT output through KRST (pulse) enable

5-4 Reserved

3-0 Select the interrupt level (note1) for WDT.

Watch Dog Timer Time-Out Value Register (Index=73h, Default=00h)

Bit Description

7-0 WDT time-out value 7-0