2 access to the smc-controller, 1 smc standard receiver format (write cycle), 1 smc – ADLINK CoreExpress-ECO2 User Manual

Page 8

2 ACCESS TO THE SMC-CONTROLLER

The communication to the SMC-Controller is done through the SMBus 1.0-compliant host controller

of the Chipset. This host controller provides a mechanism for the CPU to initiate communications

with the SMC as slave device. Please look at the Chipset Datasheet for detailed information about

the SMBus host controller. The SMC slave address is 0101000X, where X is the Read(1)-/Write(0)-

bit.

BITS

A7

A6

A5

A4

A3

A2

A1

A0

0

1

0

1

0

0

0

Read/Write

2.1 SMC

STANDARD

RECEIVER

FORMAT

(

WRITE

CYCLE

)

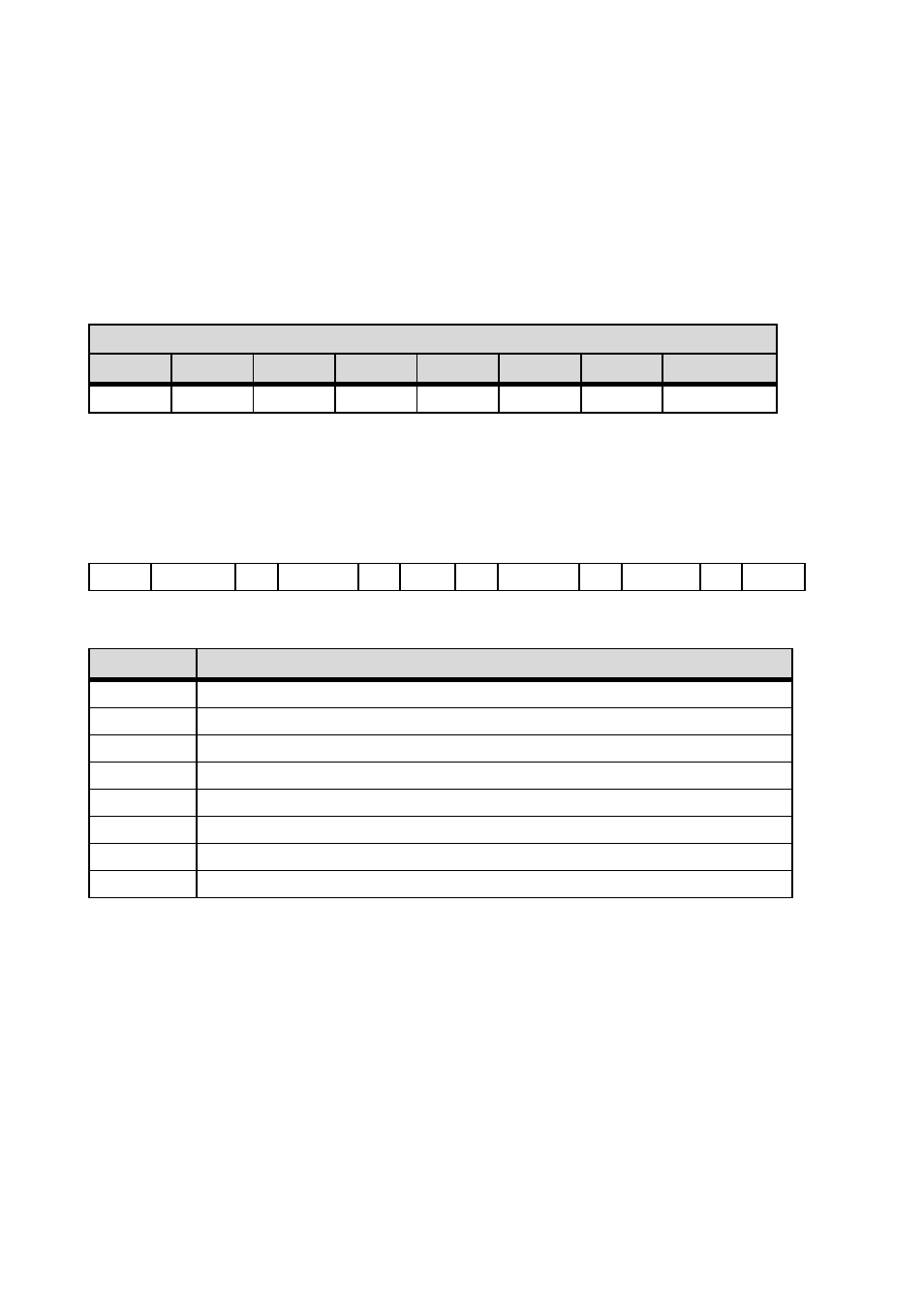

The SMC receiver format is shown in Table 2.1.1.

START SMC_addr ACK command ACK length ACK data_byte ACK n-bytes

ACK STOP

Table 2.1.1 SMC receiver format

ITEM

DESCRIPTION

START

SM-bus start condition

SMC_addr

0x50 (8-bit) (send by chipset)

ACK

SM-bus acknowledge by SMC

command

Selected Command (send by chipset)

length

Number of Data-bytes (send by chipset)

Data_byte

data byte transmitted to SMC receiver (send by chipset)

n-bytes

more data bytes transmitted to SMC receiver (send by chipset)

STOP

SM-bus stop condition

Table 2.1.2 Explanation of Table 2.1.1