5 adc and dac timing control, 1 timebase architecture, Figure 3-6: pci-9527 timebase architecture – ADLINK PCI-9527 User Manual

Page 47: 2 dds timing vs adc/dac relationship, Adc and dac timing control, Timebase architecture, Dds timing vs adc/dac relationship

Operation Theory

35

ADLINK Technology Inc.

Copyright 2010

3.5

ADC and DAC Timing Control

3.5.1

Timebase Architecture

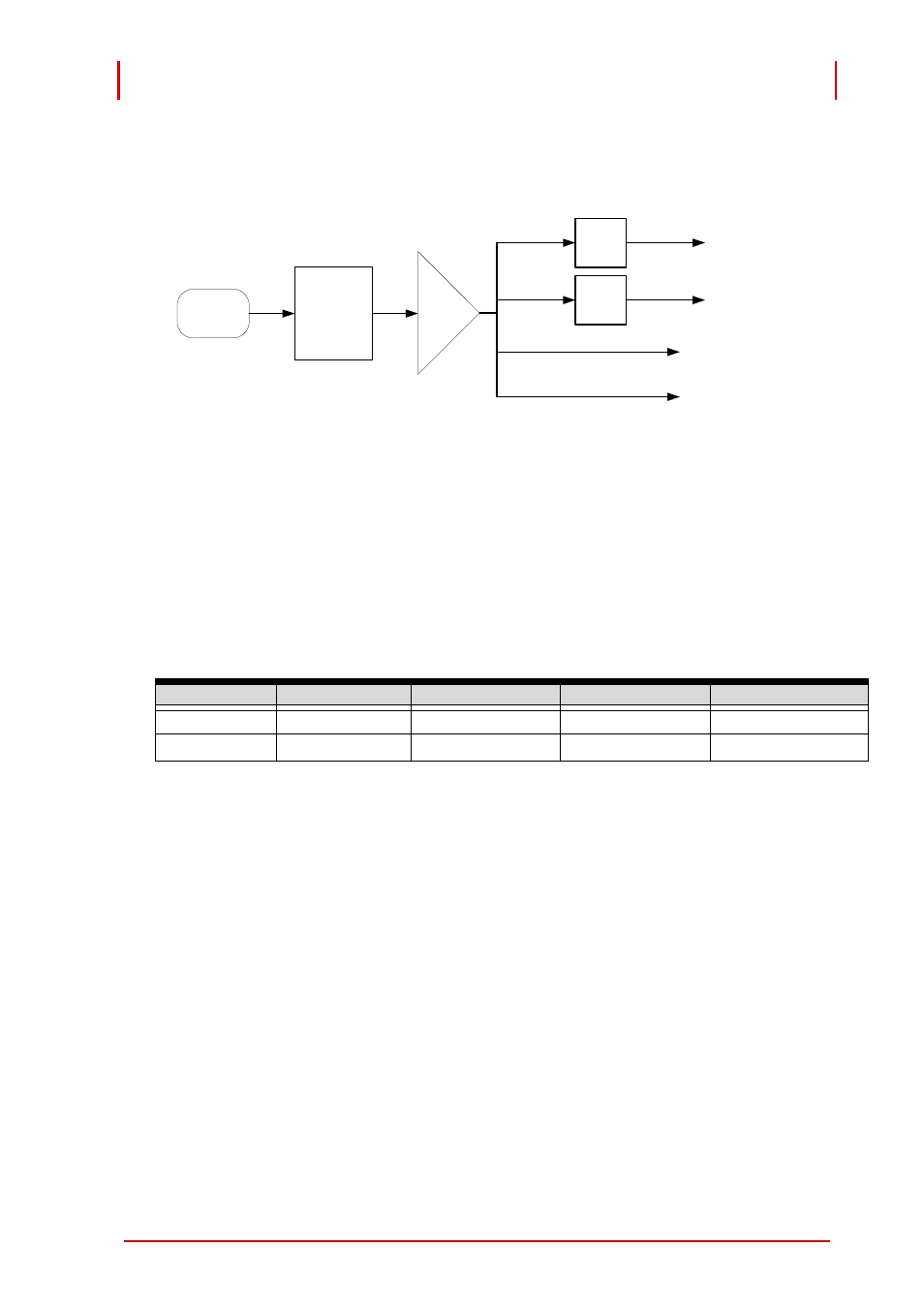

Figure 3-6: PCI-9527 Timebase Architecture

To drive the sigma-delta ADC and DAC, an onboard timebase

clock is applied. The timebase clock frequency is much higher

than the sample rate and is produced from a DDS chip. The output

frequency of DDS chip is programmable with excellent resolution.

3.5.2

DDS Timing VS ADC/DAC Relationship

Sampling Rate

2 K - 54 KHz

54 K - 108 KHz

108 K - 216 KHz

216 K - 432 KHz

Update Rate

1K-27KHz

27K-54KHz

54K-108KHz

108K-216KHz

DDS CLK

512K-13.824MHz 6.912M-13.824MHz 6.912M-13.824MHz 13.824M-27.648MHz

Table 3-7: Timing Relationship of the ADC, DAC and DDS Clock

DAC CH1

Onboard

125MHz

Oscillator

ADC CH0

ADC CH1

DAC CH0

1-

to

-4 Clock

Bu

ff

er

DDS

½

Divider

½

Divider

Resolution equal to

125MHz/2^32 = 0.029Hz