3 digital output register (base + 14), 4 dio status & control register (base + 18), Digital output register (base + 14) – ADLINK PCI-7200 User Manual

Page 38: Dio status & control register (base + 18)

26

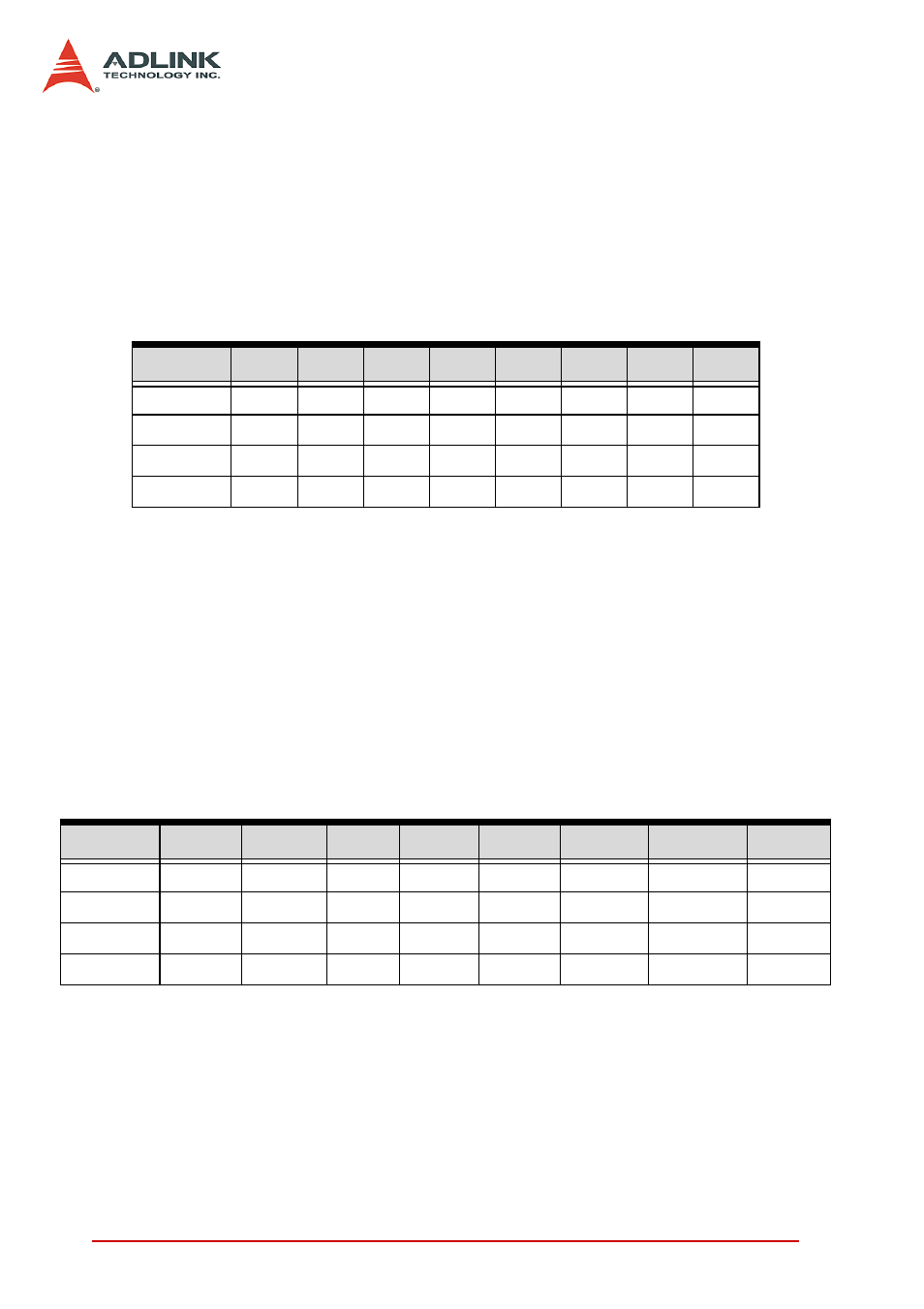

Register Format

3.3 Digital Output Register (BASE + 14)

32 digital output channels can be written and read to/from this reg-

ister

Address: BASE + 14

Attribute: READ/WRITE

Data Format:

The digital output status can be read back through the same loca-

tion (BASE + 14)

3.4 DIO Status & Control Register (BASE + 18)

The data transfer mode of digital input is controlled and status is

checked through this register.

Address: BASE + 18

Attribute: READ/WRITE

Data Format:

X

Digital Input Mode Setting:

I_ACK: Input ACK Enable

1: Input ACK is enabled (input ACK will be asserted after in-

put data is read by CPU or written to input FIFO)

0: Input ACK is disabled

Byte

7

6

5

4

3

2

1

0

Base +14 DO7

DO6

DO5

DO4

DO3

DO2

DO1

DO0

Base +15 DO15 DO14 DO13 DO12 DO11 DO10 DO9

DO8

Base +16 DO23 DO22 DO21 DO20 DO19 DO18 DO17 DO16

Base +17 DO31 DO30 DO29 DO28 DO27 DO26 DO25 DO24

Byte

7

6

5

4

3

2

1

0

Base +18 O_ACK DIN_EN I_TRG TRGPL I_FIFO I_TIME0

I_REQ

I_ACK

Base +19

----

I_OVER

----

----

O_TRG O_FIFO O_TIME1 O_REQ

Base +20

----

----

----

----

----

----

----

O_UND

Base +21

----

----

----

----

----

----

----

----