ADLINK PCI-7300A User Manual

Page 48

40

• Operation Theory

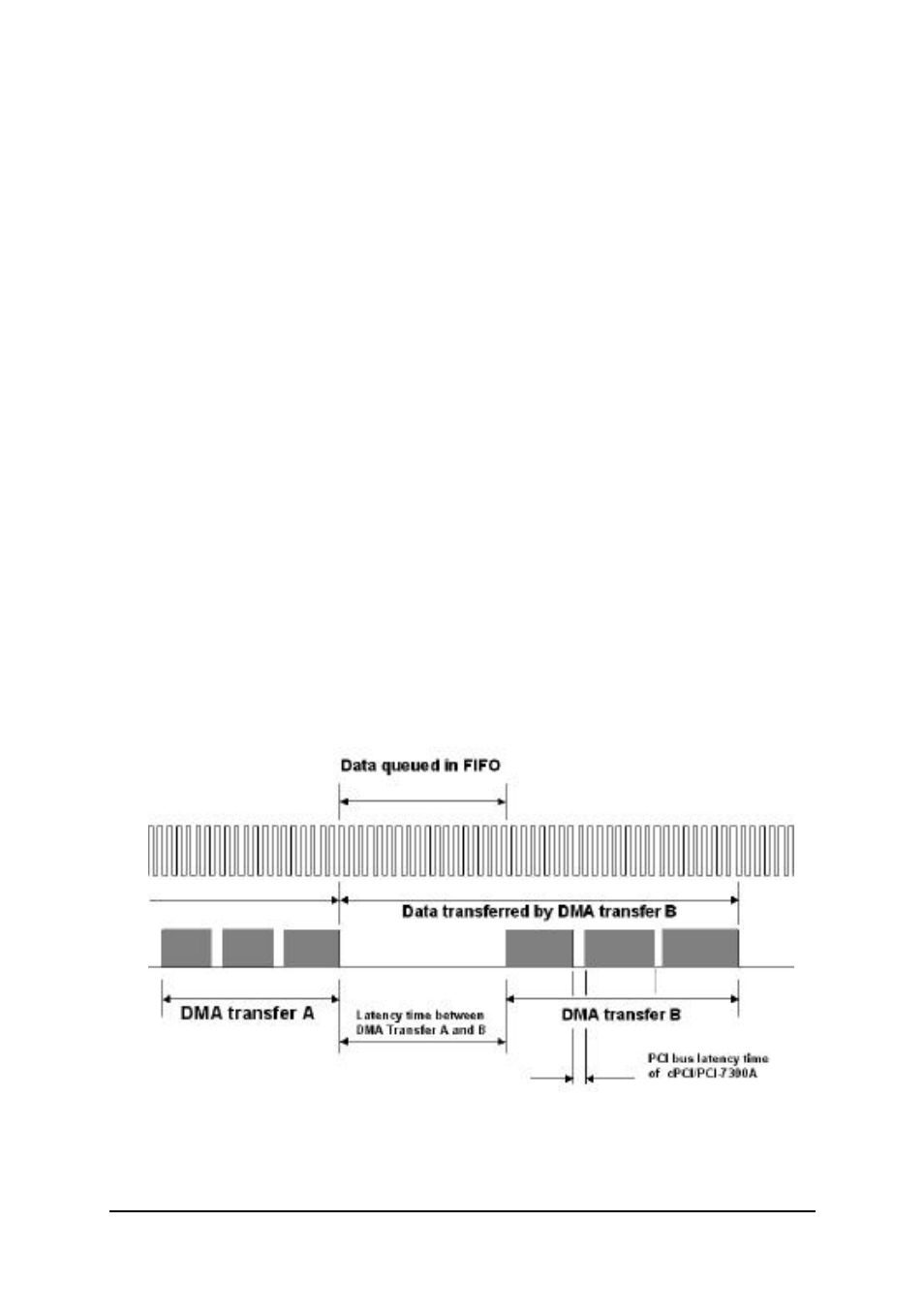

4.10.4 Continuous Digital Input

If the digital input operation still active after the competition of the previous

DMA transfer and do not clear the data in the input FIFO when the next DMA

starts, the cPCI/PCI-7300A can achieve the continuous digital input function in

a high-speed sampling rate. In this case, the input FIFO buffers the input data

and waits for the next DMA to move the queued data to the system memory.

To avoid the overrun of input FIFO causes the data lost of the continuous

digital input, the latency time of the next DMA should be smaller than the time

to overrun the input FIFO. There are some rules of thumb should be mentioned

here:

1. The lower the sampling frequency is, the longer the time to overrun the input

FIFO is. That means the fewer overrun situations will occur.

2. To reduce the latency time between two DMA transfers, please disable

unnecessary PCI bus mastering devices, and remove the unnecessary

processes in your application programs.

3. When high-speed sampling frequency is applied, the larger block size will

improve the efficiency of DMA transferring, and probability of overrun in the

DMA process will be reduced.

4. To apply the high-speed continuous digital input, it is recommended to

execute your application programs in the non-multitask operation system to

reduce the latency time between two DMA transfers.