Hardware description, Connector pinouts – Connect Tech PCI-104 User Manual

Page 38

Connect Tech FreeForm/PCI-104 User Manual

Revision 0.02

38

Hardware Description

Connector Pinouts

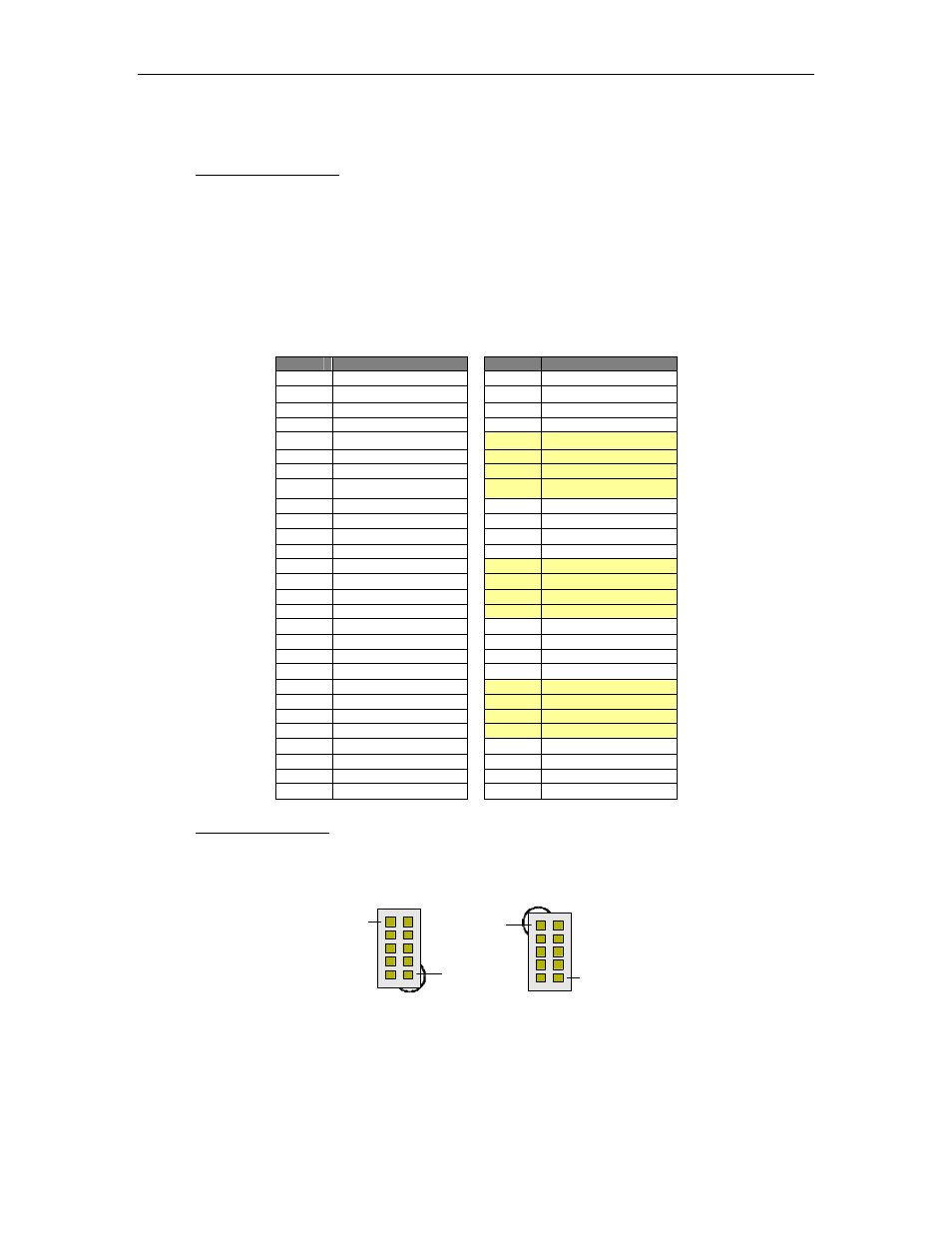

High-speed Serial (P4)

The sideband LVCMOS signals (HSS) have been rearranged so that when two FreeForm units are

connected:

HSS_USER_IO(0) maps to HSS_USER_IO(2)

HSS_USER_IO(1) maps to HSS_USER_IO(3)

Also, 3.3V pins replace the GND pins; this is because the connector has embedded GND blades.

Revision B

Revision C

Pin

Signal

1

MTGRXN0_112

3

MTGRXP0_112

2

MTGTXN0_112

4

MTGTXP0_112

5

GND

7

GND

6

HSS_USER_IO(0)

8

HSS_USER_IO(1)

9

MTGRXN1_112

11

MTGRXP1_112

10

MTGTXN1_112

12

MTGTXP1_112

13

GND

15

GND

14

GND

16

GND

17

MTGRXN0_114

19

MTGRXP0_114

18

MTGTXN0_114

20

MTGTXP0_114

21

GND

23

GND

22

HSS_USER_IO(2)

24

HSS_USER_IO(3)

25

MTGRXN1_114

27

MTGRXP1_114

26

MTGTXN1_114

28

MTGTXP1_114

Pin

Signal

1

MTGRXN0_112

3

MTGRXP0_112

2

MTGTXN0_112

4

MTGTXP0_112

5

HSS_USER_IO(0)

7

HSS_USER_IO(1)

6

HSS_USER_IO(2)

8

HSS_USER_IO(3)

9

MTGRXN1_112

11

MTGRXP1_112

10

MTGTXN1_112

12

MTGTXP1_112

13

3.3V

15

3.3V

14

3.3V

16

3.3V

17

MTGRXN0_114

19

MTGRXP0_114

18

MTGTXN0_114

20

MTGTXP0_114

21

3.3V

23

3.3V

22

3.3V

24

3.3V

25

MTGRXN1_114

27

MTGRXP1_114

26

MTGTXN1_114

28

MTGTXP1_114

RS-485 Headers (P5)

The orientation of the connector has changed. The pinout remains the same.

Revision B

Revision C

1

10

P5

485 Port 0

1

P5

10

485 Port 0