Power and thermal considerations, Reference design fpga power analysis – Connect Tech PCI-104 User Manual

Page 20

Connect Tech FreeForm/PCI-104 User Manual

Revision 0.02

20

Power and Thermal Considerations

The FreeForm/PCI-104’s Virtex-5 FPGA is a versatile, flexible device, with many built-in features like

termination, PLLs, and high speed gigabit transceivers. The drawback of these on-chip features is that they

consume a lot of power and hence dissipate a lot of heat.

As a result Connect Tech, is recommending the installation of a heatsink, included with the product (see

section

). As well, the FPGA designer must perform power analysis on their design to

determine that they are not stressing the Virtex-5 component (i.e. exceeding the junction temperature).

Power analysis can be performed using the Xpower Analyzer (part of the ISE design suite) and the XPE

spreadsheets (Xilinx Power Estimator Spreadsheets).

Reference Design FPGA power analysis

Power analysis was performed on the FCG001 when configured with the reference design. The Virtex-

5 XPE spreadsheet was used to determine an effective junction to ambient thermal resistance

(θ

JA_effective

). The following parameters are entered into the spreadsheet to determine θ

JA_effective.

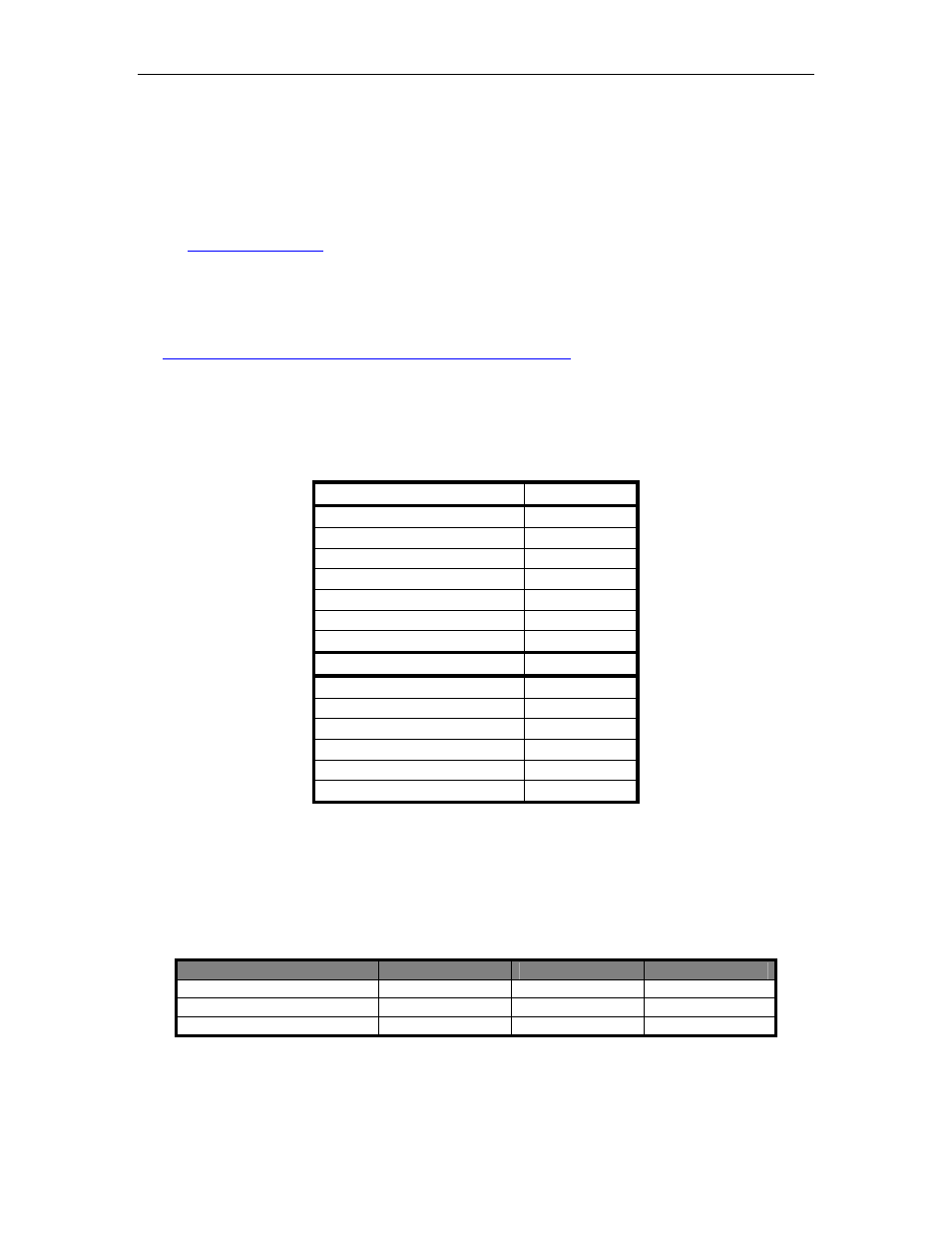

Device

Part

XC5VLX30T

Package

FF665

Grade

Industrial

Process

Typical

Speed Grade

-1

Stepping

Stepping - 1

Thermal Information

Ambient Temp (°C)

50

Airflow (LFM)

250

Heat Sink

Custom

Custom ΘSA (°C/W)

8 (*)

Board Selection

Small (4"x4")

# of Board Layers

12 to 15

(θ

SA

is the surface to ambient temperature for a heatsink with dimensions 27 mm x 27 mm x 6.4 mm and 250 LFM airflow. The

θ

SA

improves (decreases) with a taller heatsink. )

Three scenarios were developed and the XPE parameters Airflow and Custom ΘSA were varied. The

θ

JA_effective

was entered into the Xpower Analyzer yielding a Juction Temperature @ 50 °C and a

maximum ambient temperature. The following table summarizes the scenarios and the results. For

complete details of the scenarios, see Appendix B.

Scenario

θ

JA_effective

(°C/W)

T

ambient_max

T

junction

at 50 °C

Heatsink attached, 250 LFM

4.9

82.7

67.3

No Heatsink, 250 LFM

6.4

72.7

72.7

No heatsink, 0 LFM

9.7

65.1

84.9

Calculation details:

T

junction

= T

ambient

+ (P

FPGA

* θ

JA_effective

)

= 50°C + (3.53W * 4.9 °C /W) = 67.297°C

T

ambient_max

= T

junction_max

- (P

FPGA

* θ

JA_effective

) = 100°C - (3.53W * 4.9 °C /W) = 82.7°C

Note T

junction_absolute_max

= 125°C is not used, since this is the absolute point of failure.