Aw2400mspi user’s manual – AvaLAN Wireless AW2400mSPI-10 User Manual

Page 25

PAGE 25

Technical support (650) 384-0000

www.avalanwireless.com

AW2400mSPI

User’s Manual

code, here is how to do it.

The following information applies to SPI Mode only:

Once a

setFirmwareStart (0x8B) command has been issued to the XC1220, all other

commands except for

setPacket (0x8A) and setFirmwareEnd (0x8C) become in-

valid and will cause the Error Flag to assert if they are issued. The host microcon-

troller must deassert the /CS_BB line (pin 12) and then wait for a minimum of 5 µs

and the DATA Ready line (pin 9) to be asserted before reasserting /CS_BB to send

the first data block.

The firmware image is partitioned into data blocks with a payload size of 64 bytes.

Each block is sent as it’s own transaction and must use the

setPacket command to

be issued to the XC1220. Since data can be submitted to the XC1220 faster than it

can be stored in flash, the FIFO Full line must be carefully observed to make sure

none of the blocks are lost.

If the last firmware block is not a full 64 bytes, it must be padded with zeros.

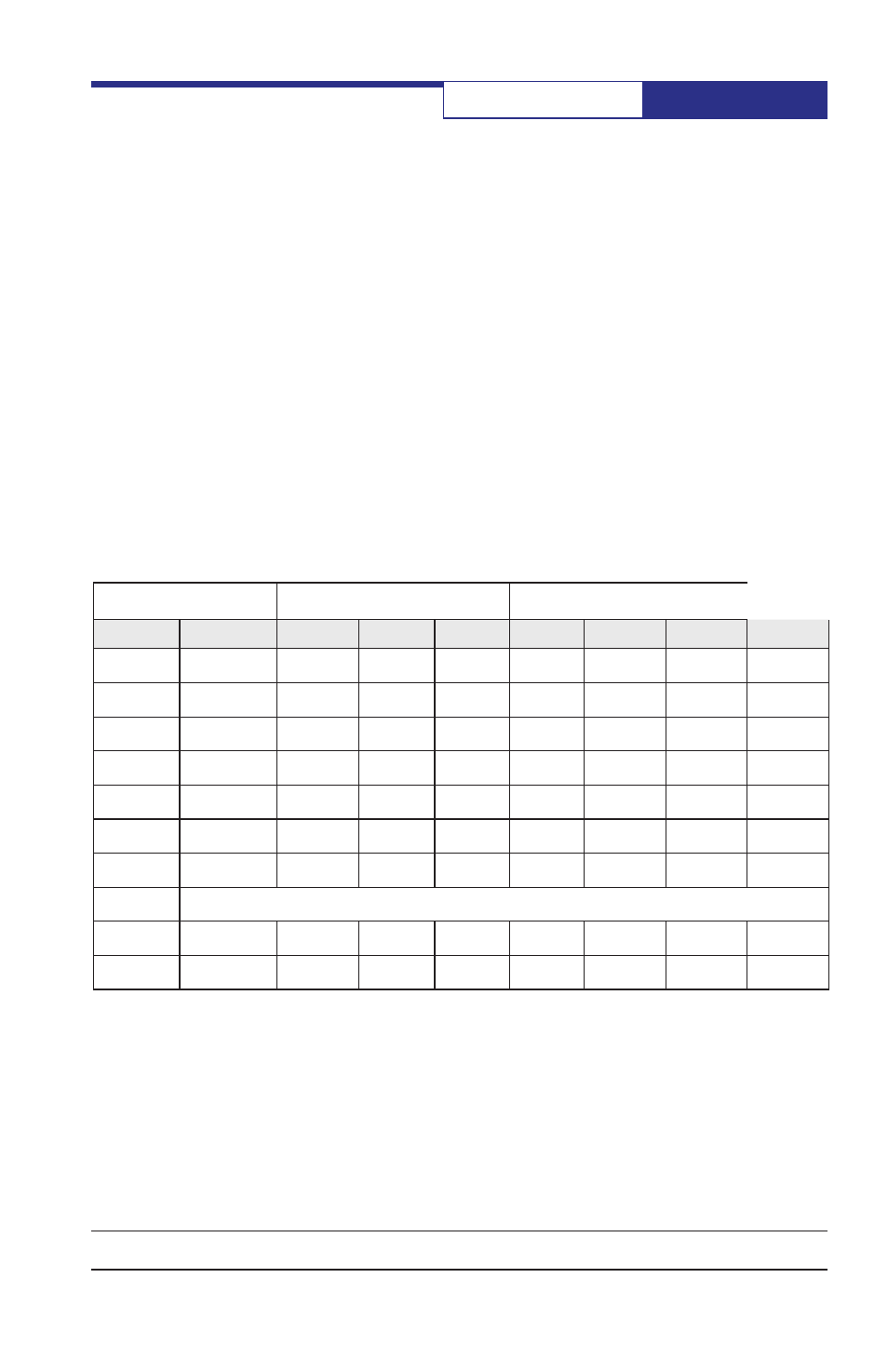

setPacket

SPI Mode:

0x8A

b7

b6

b5

b4

b3

b2

b1

b0

Byte 1

BC

ID6

ID5

ID4

ID3

ID2

ID1

ID0

Byte 2

S7

S6

S5

S4

S3

S2

S1

S0

Byte 3

-

-

-

-

-

S10

S9

S8

Byte 4

OFS7

OFS6

OFS5

OFS4

OFS3

OFS2

OFS1

OFS0

Byte 5

OFS15

OFS14

OFS13

OFS12

OFS11

OFS10

OFS9

OFS8

Byte 6

DATA7

DATA6

DATA5

DATA4

DATA3

DATA2

DATA1

DATA0

Byte 7

DATA15

DATA14 DATA13 DATA12 DATA11 DATA10

DATA9

DATA8

...

Bytes 6 and 7 are repeated 32 times.

Byte 70

CHK7

CHK6

CHK5

CHK4

CHK3

CHK2

CHK1

CHK0

Byte 71

CHK15

CHK14

CHK13

CHK12

CHK11

CHK10

CHK9

CHK8

BC must be set and ID0 to ID6 must be clear. (Byte 1 is 0x80.)

S0 to S10 must be set to 68. (Byte 2 is 0x44 and Byte3 is 0x00.)

OFS0 to OFS15 is the 16-bit integer firmware block number. This value will be in-

cluded in the checksum calculation.

DATA0 to DATA15 is the 16-bit firmware data, 32 values per block.