2 connector x4 (signal levels), Connector x4 (signal levels), Etx-oh / etx® connectors – Kontron ETX-OH User Manual

Page 44

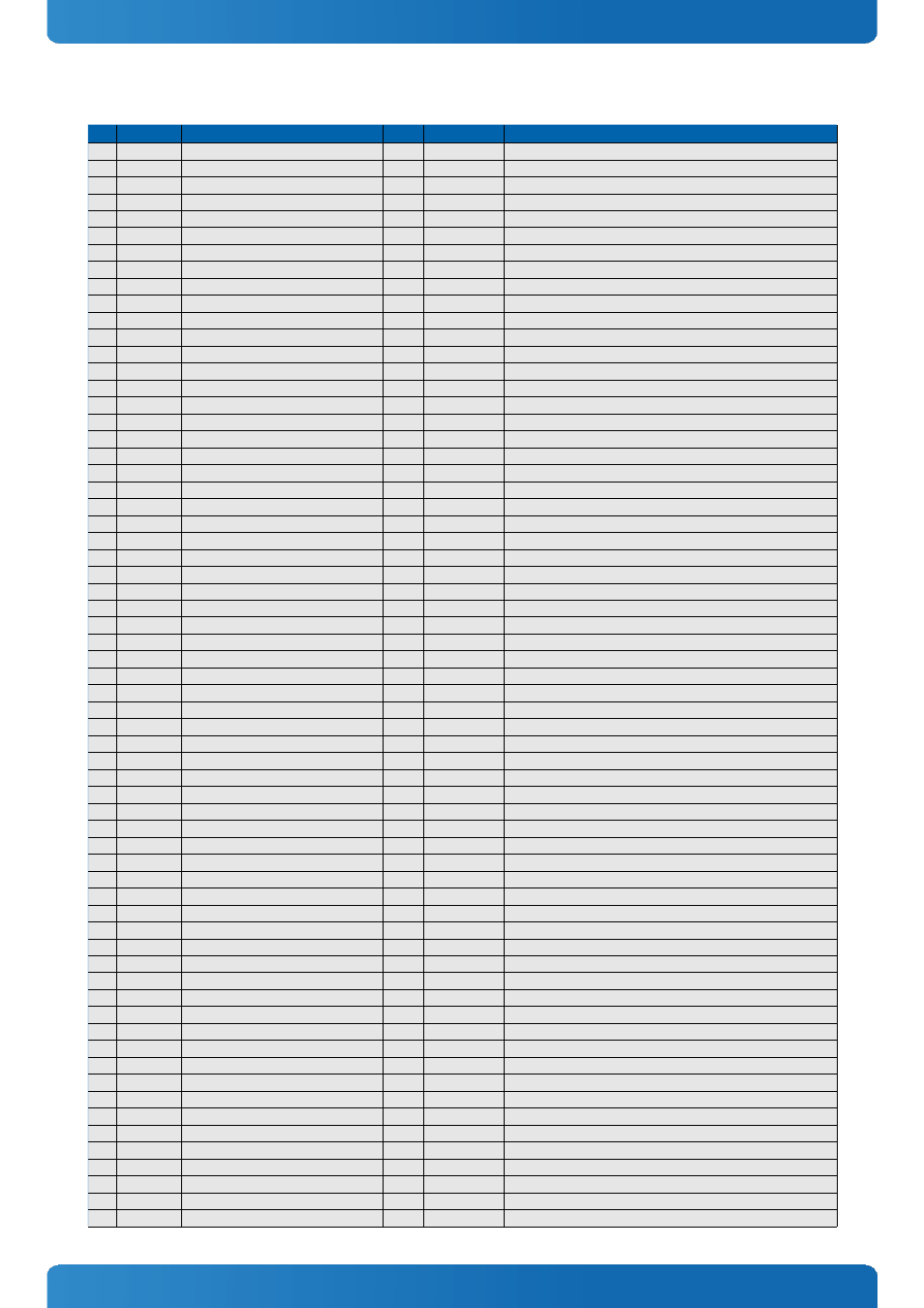

ETX-OH / ETX® Connectors

6.4.2

Connector X4 (Signal Levels)

Pin Signal

Description

Type

Termination

Comment

1

GND

Ground

PWR

-

-

2

GND

Ground

PWR

-

-

3

5V_SB

Supply of internal suspend Circuit

PWR

-

-

4

PWGIN

Power Good / Reset Input

I-3,3

PU 4k7 3,3V_SB 5V tolerant

5

PS_ON

Power Supply On

O-5

PU 4k7 5V

-

6

SPEAKER

Speaker Output

O-3,3

-

-

7

PWRBTN#

Power Button

I-5

PU 5k 5V

-

8

BATT

Battery Supply

PWR

-

-

9

KBINH

Keyboard Inhibit Control Input

nc

-

Not supported

10

LILED

Ethernet Link LED

O

-

Open collector

11

RSMRST#

Resume Reset

I-3,3

PU 4k7 3,3V

5V tolerant

12

ACTLED

Ethernet Activity LED

O

-

Open collector

13

ROMKBCS#

-

O-5

PU 10k 5V

Not supported

14

SPEEDLED

Ethernet Speed LED

O

-

Open collector

15

EXT_PRG

-

nc

-

Not supported

16

I2CLK

I2C Bus Clock

O-5

PU 2k2 5V

-

17

VCC

Power +5V

PWR

-

-

18

VCC

Power +5V

PWR

-

-

19

OVCR#

Over Current Detect for USB

I-3,3

PU 10k 3,3V

-

20

GPCS#

-

O-5

PU 10k 5V

Not supported

21

EXTSMI#

System Management Interrupt Input

I-3,3

PU 4k7 3,3V

5V tolerant

22

I2DAT

I2C Bus Data

IO-5

PU 2k2 5V

-

23

SMBCLK

SM Bus Clock

O-3,3

PU 2k2 3,3V

-

24

SMBDATA

SM Bus Data

IO-3,3 PU 2k2 3,3V

-

25

SIDE_CS3#

Secondary IDE Chip Select Channel 1

O-3,3

-

-

26

SMBALRT#

SMB Alert

I-3,3

PU 2k2 3,3V

-

27

SIDE_CS1#

Secondary IDE Chip Select Channel 1

O-3,3

-

-

28

DASP_S

-

nc

-

Not supported

29

SIDE_A2

Secondary IDE Adress Bus

O-3,3

-

-

30

PIDE_CS3#

Primary IDE Chip Select Channel 1

O-3,3

-

-

31

SIDE_A0

Secondary IDE Adress Bus

O-3,3

-

-

32

PIDE_CS1#

Primary IDE Chip Select Channel 0

O-3,3

-

-

33

GND

Ground

PWR

-

-

34

GND

Ground

PWR

-

-

35

PDIAG_S

Secondary IDE CBLID#

I-3,3

PD 100k

-

36

PIDE_A2

Primary IDE Adress Bus

O-3,3

-

-

37

SIDE_A1

Secondary IDE Adress Bus

O-3,3

-

-

38

PIDE_A0

Primary IDE Adress Bus

O-3,3

-

-

39

SIDE_INTRQ Secondary IDE Interrupt Reqeuest

I-3,3

PD 10k

-

40

PIDE_A1

Primary IDE Adress Bus

O-3,3

-

-

41

BATLOW#

Battery Low

I-3,3

PU 4k7 3,3V

5V tolerant

42

GPE1#

General Purpose Power Event 1

I-3,3

-

5V tolerant, pin GEVENT5# with int. PU 8k2 in A55E

43

SIDE_AK#

Secondary IDE DMA Acknowledge

O-3,3

-

-

44

PIDE_INTRQ Primary IDE Interrupt Reqeuest

I-3,3

PD 10k

-

45

SIDE_RDY

Secondary IDE Ready

I-3,3

PU 4k7 3,3V

-

46

PIDE_AK#

Primary IDE DMA Acknowledge

O-3,3

-

-

47

SIDE_IOR#

Secondary IDE IO Read

O-3,3

-

-

48

PIDE_RDY

Primary IDE Ready

I-3,3

PU 4k7 3,3V

-

49

VCC

Power +5V

PWR

-

-

50

VCC

Power +5V

PWR

-

-

51

SIDE_IOW#

Secondary IDE IO Write

O-3,3

-

-

52

PIDE_IOR#

Primary IDE IO Read

O-3,3

-

-

53

SIDE_DRQ

Secondary IDE DMA Request

I-3,3

PD 5k6

-

54

PIDE_IOW#

Primary IDE IO Write

O-3,3

-

-

55

SIDE_D15

Secondary IDE Data Bus

IO-3,3 -

-

56

PIDE_DRQ

Primary IDE DMA Request

I-3,3

PD 5k6

-

57

SIDE_D0

Secondary IDE Data Bus

IO-3,3 -

-

58

PIDE_D15

Primary IDE Data Bus

IO-3,3 -

-

59

SIDE_D14

Secondary IDE Data Bus

IO-3,3 -

-

60

PIDE_D0

Primary IDE Data Bus

IO-3,3 -

-

61

SIDE_D1

Secondary IDE Data Bus

IO-3,3 -

-

62

PIDE_D14

Primary IDE Data Bus

IO-3,3 -

-

63

SIDE_D13

Secondary IDE Data Bus

IO-3,3 -

-

64

PIDE_D1

Primary IDE Data Bus

IO-3,3 -

-

44