Pci express root port 0/1/2/3 – Kontron COMe-mCT10 User Manual

Page 95

COMe-mCT10 / BIOS Operation

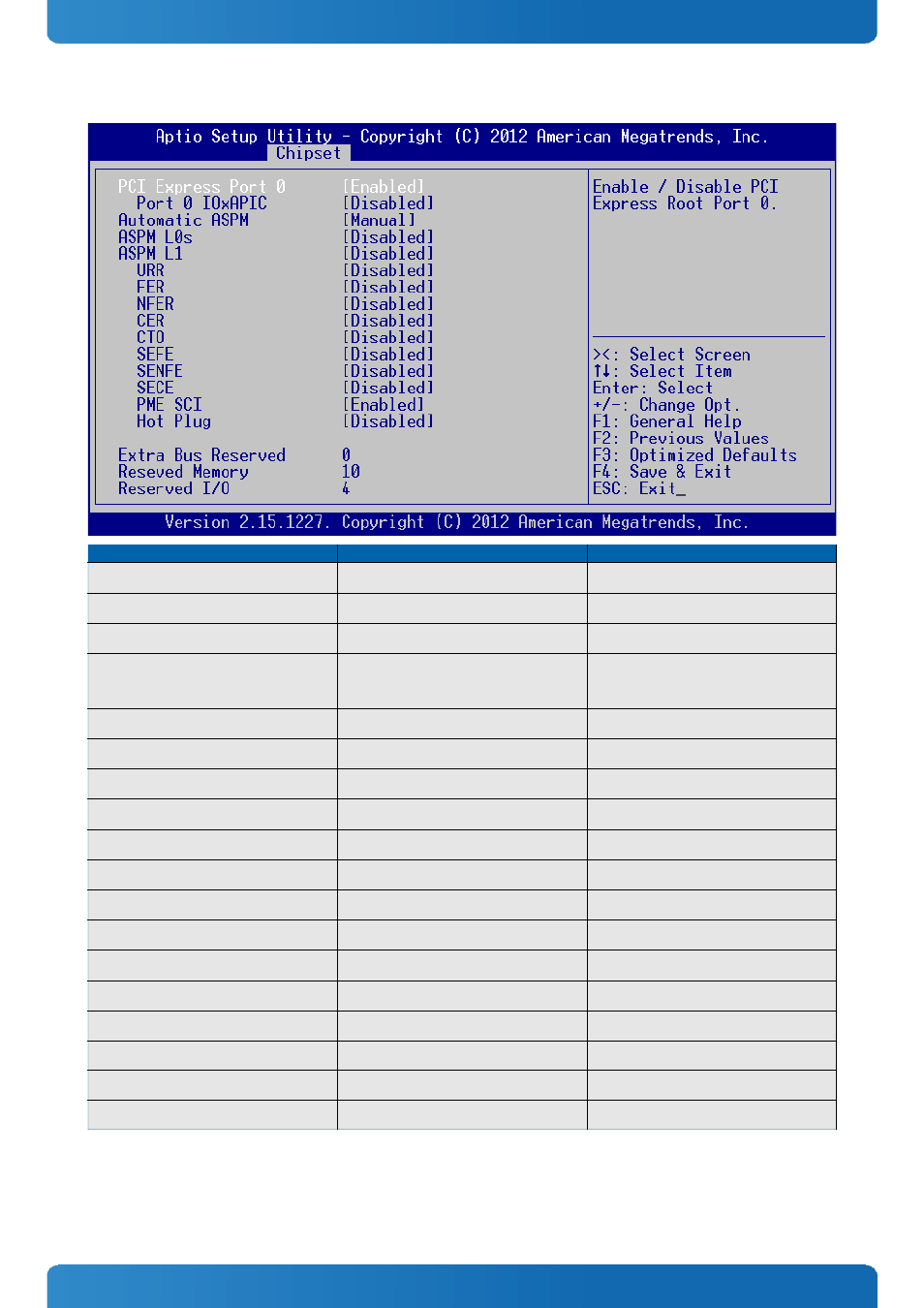

PCI Express Root Port 0/1/2/3

Feature

Options

Description

PCI Express Root Port

Disabled

Enabled

Enable/Disable the PCI Express Root Port

Port x IOxAPIC

Disabled

Enabled

Enable/Disable PCI Express Root Port I/O APIC

Automatic ASPM

Manual

Auto

Automatically enable ASPM based on reported

capabilities and known issues

ASPM L0s

Disabled

Root Port Only

Endpoint Port Only

Both Root And Endpoint Ports

Enable PCIe ASPM L0s

ASPM L1

Disabled

Enabled

Enable PCIe ASPM L1

URR

Disabled

Enabled

Enable or Disable PCI Express Unsupported Request

Reporting

FER

Disabled

Enabled

Enable or Disable PCI Express Device Fatal Error

Reporting

NFER

Disabled

Enabled

Enable or Disable PCI Express Device Non-Fatal Error

Reporting

CER

Disabled

Enabled

Enable or Disable PCI Express Device Correctable Error

Reporting

CTO

Disabled

Enabled

Enable or Disable PCI Express Completion Timer Timeout

SEFE

Disabled

Enabled

Enable or Disable Root PCI Express System Error on

Fatal Error

SENFE

Disabled

Enabled

Enable or Disable Root PCI Express System Error on Non-

Fatal Error

SECE

Disabled

Enabled

Enable or Disable Root PCI Express System Error on

Correctable Error

PME SCI

Disabled

Enabled

Enable or Disable PCI Express PME SCI

Hot Plug

Disabled

Enabled

Enable or Disable PCI Express Hot Plug

Extra Bus Reserved

0

Extra Bus Reserved (0-7) for bridges behind this Root

Bridge

Reserved Memory

10

Reserved Memory and Prefetchable Memory (1-20 MB)

Range for this Root Bridge

Reserved I/O

4

Reserved I/O (4k/8k(12k/16k/20k) Range for this Root

Bridge

95