Cpld & post-code display, 17 cpld & post-code display – Kontron COMe Eval Carrier T10 User Manual

Page 41

COM Express® Eval Type 10

/ Connectors and Features

38

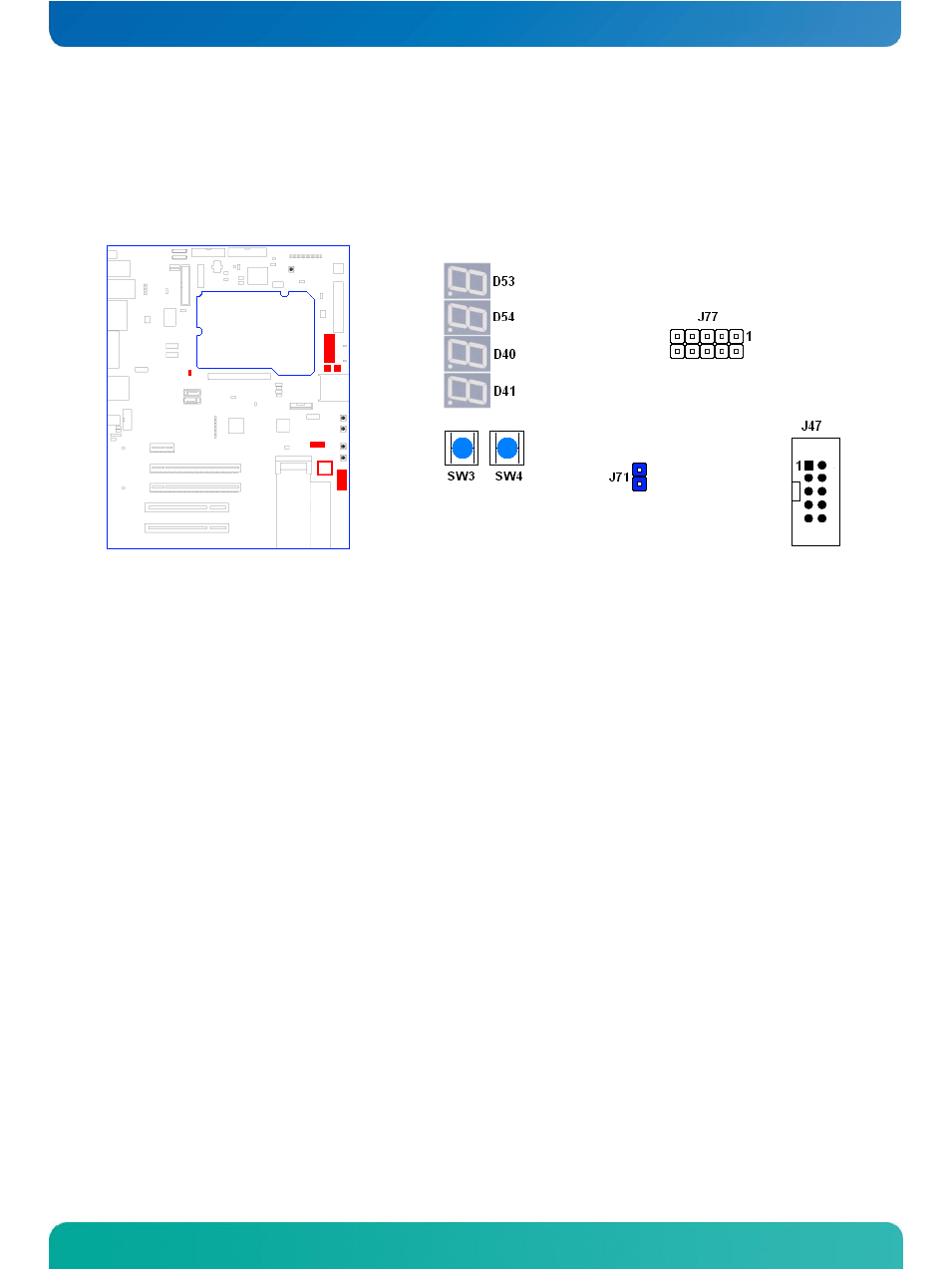

5.17 CPLD & POST-Code Display

Power Management control, 4 digits LPC/PCI Port 80/81 Post Code and additional GPIOs are implemented in onboard

Altera CPLD (U44).

Port 80/81 POST Code display

The 7-segment display D53/D54 for Port 81 and D40/41 for Port 80 shows BIOS status codes during boot-up process.

Last 8 check codes are stored automatically and can be controlled by switch SW3 (Post Code step backward) and

switch SW4 (Post code step forward). Pressing SW3 and SW4 simultaneously returns to newest POST code.

The POST Code display also shows current Suspend state:

»

S3

-> POST code "_ _ _ 3"

»

S4

-> POST code "_ _ _ 4"

»

S5

-> POST code "_ _ _ 5"

Power Good J71

The Power Good output generated by the CPLD must be high level to allow the module to start. Some modules may

provide direct power-on support if VCC gets connected and PWR_OK (COM Exress pin B24) is open or at high level. To

test this functionality configuration jumper J71 can be opened to disconnect Power Good.