16 shared graphics interfaces, Shared graphics interfaces, Come-bip2 / features and interfaces – Kontron COMe-bIP2 User Manual

Page 47

COMe-bIP2 / Features and Interfaces

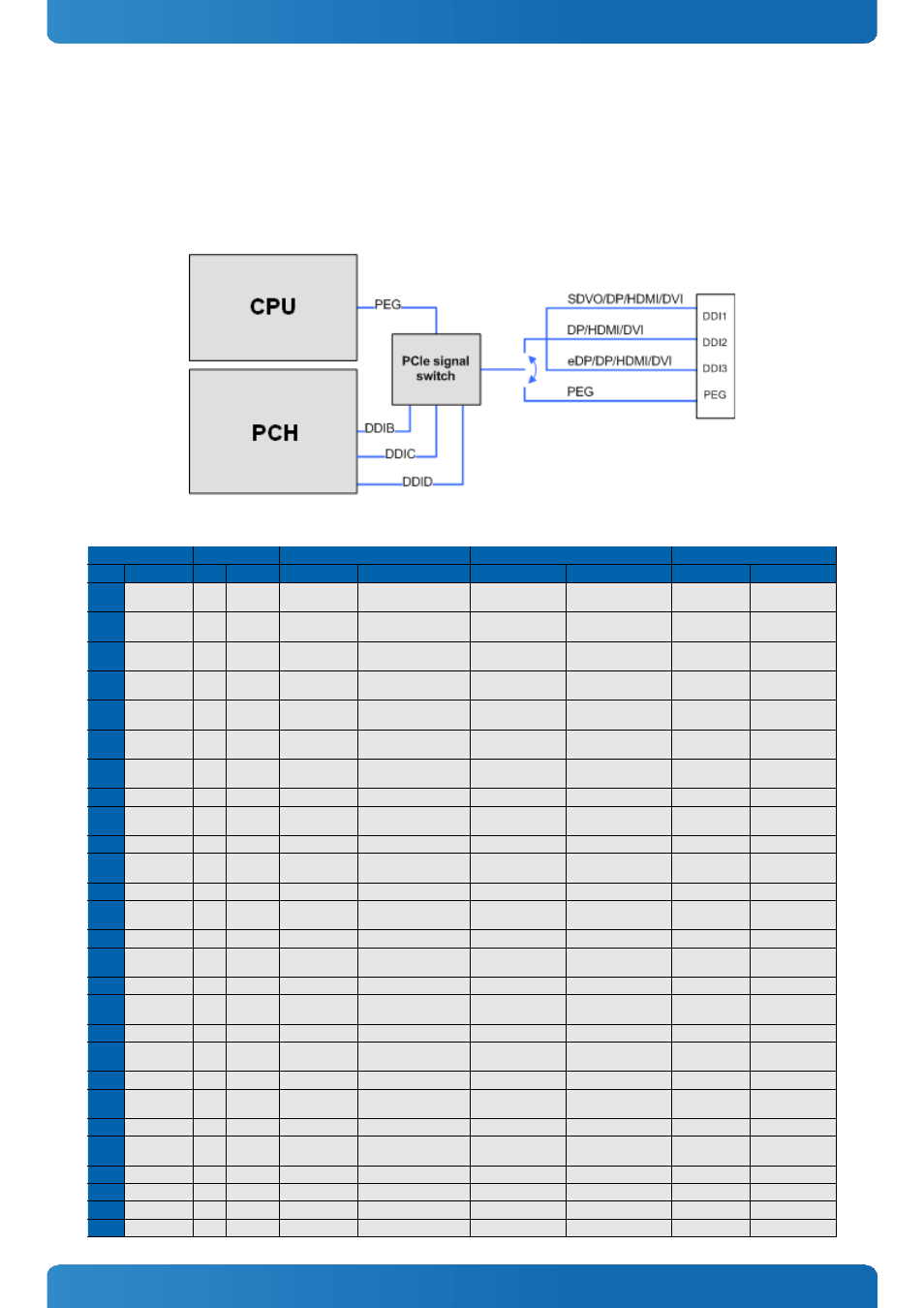

4.16 Shared Graphics Interfaces

On COM Express® pin-out Type 2 based Computer-on-Modules the PCI Express Graphics interface is usually multiplexed

with several digital display interfaces like SDVO, DisplayPort, HDMI or TMDS if supported by the chipset. The new

generation Chief River platform no longer shares it's interfaces. For full backwards compatibility the COMe-bIP2 includes

multi-staged PCIexpress 2.0 switches to provide a shared graphics output on PEG Interface similar to former platforms. It

offers full functionality like auto detection for external Graphics or SDVO devices.

PEG Interface pin-outs

COM Express

x16 PCI Express

SDVO

HDMI & DVI

Display Port

Pin

Name

Pin

Name

Pin name

Description

Pin name

description

pin name

description

D52

PEG_TX[0]+

B14

HSOp(0)

SDVOB_RED_P

Digital Video B red

TMDS_B_DATA2_P

HDMI Port B Data2

DPB_LANE0_P

DisplayPort B

Lane0 output

D53

PEG_TX[0]-

B15

HSOn(0)

SDVOB_RED_N

output differential pair TMDS_B_DATA2_N

output differential

pair

DPB_LANE0_N

differential pair

D55

PEG_TX[1]+

B19

HSOp(1)

SDVOB_GRN_P

Digital Video B green

TMDS_B_DATA1_P

HDMI Port B Data1

DPB_LANE1_P

DisplayPort B

Lane1 output

D56

PEG_TX[1]-

B20

HSOn(1)

SDVOB_GRN_N output differential pair TMDS_B_DATA1_N

output differential

pair

DPB_LANE1_N

differential pair

D58

PEG_TX[2]+

B23

HSOp(2)

SDVOB_BLU_P

Digital Video B blue

TMDS_B_DATA0_P

HDMI Port B Data0

DPB_LANE2_P

DisplayPort B

Lane2 output

D59

PEG_TX[2]-

B24

HSOn(2)

SDVOB_BLU_N

output differential pair TMDS_B_DATA0_N

output differential

pair

DPB_LANE2_N

differential pair

D61

PEG_TX[3]+

B27

HSOp(3)

SDVOB_CK_P

Digital Video B clock

TMDS_B_CLK _P

HDMI Port B Clock

output

DPB_LANE3_P

DisplayPort B

Lane3 output

D62

PEG_TX[3]-

B28

HSOn(3)

SDVOB_CK_N

differential pair

TMDS_B_CLK _N

differential pair

DPB_LANE3_N

differential pair

D65

PEG_TX[4]+

B33

HSOp(4)

-

-

TMDS_C_DATA2_P

HDMI Port C Data2

output

DPC_LANE0_P

DisplayPort C

Lane0 output

D66

PEG_TX[4]-

B34

HSOn(4)

-

-

TMDS_C_DATA2_N

differential pair

DPC_LANE0_N

differential pair

D68

PEG_TX[5]+

B37

HSOp(5)

-

-

TMDS_C_DATA1_P

HDMI Port C Data1

output

DPC_LANE1_P

DisplayPort C

Lane1 output

D69

PEG_TX[5]-

B38

HSOn(5)

-

-

TMDS_C_DATA1_N

differential pair

DPC_LANE1_N

differential pair

D71

PEG_TX[6]+

B41

HSOp(6)

-

-

TMDS_C_DATA0_P

HDMI Port C Data0

output

DPC_LANE2_P

DisplayPort C

Lane2 output

D72

PEG_TX[6]-

B42

HSOn(6)

-

-

TMDS_C_DATA0_N

differential pair

DPC_LANE2_N

differential pair

D74

PEG_TX[7]+

B45

HSOp(7)

-

-

TMDS_C_CLK _P

HDMI Port C Clock

output

DPC_LANE3_P

DisplayPort C

Lane3 output

D75

PEG_TX[7]-

B46

HSOn(7)

-

-

TMDS_C_CLK _N

differential pair

DPC_LANE3_N

differential pair

D78

PEG_TX[8]+

B50

HSOp(8)

-

-

TMDS_D_DATA2_P

HDMI Port D Data2

output

DPD_LANE0_P

DisplayPort D

Lane0 output

D79

PEG_TX[8]-

B51

HSOn(8)

-

-

TMDS_D_DATA2_N

differential pair

DPD_LANE0_N

differential pair

D81

PEG_TX[9]+

B54

HSOp(9)

-

-

TMDS_D_DATA1_P

HDMI Port D Data1

output

DPD_LANE1_P

DisplayPort D

Lane1 output

D82

PEG_TX[9]-

B55

HSOn(9)

-

-

TMDS_D_DATA1_N

differential pair

DPD_LANE1_N

differential pair

D85

PEG_TX[10]+ B58

HSOp(10) -

-

TMDS_D_DATA0_P

HDMI Port D Data0

output

DPD_LANE2_P

DisplayPort D

Lane2 output

D86

PEG_TX[10]-

B59

HSOn(10) -

-

TMDS_D_DATA0_N

differential pair

DPD_LANE2_N

differential pair

D88

PEG_TX[11]+ B62

HSOp(11) -

-

TMDS_D_CLK _P

HDMI Port D Clock

output

DPD_LANE3_P

DisplayPort D

Lane3 output

D89

PEG_TX[11]-

B63

HSOn(11) -

-

TMDS_D_CLK _N

differential pair

DPD_LANE3_N

-

D91

PEG_TX[12]+ B66

HSOp(12) -

-

-

-

-

-

D91

PEG_TX[12]-

B67

HSOn(12) -

-

-

-

-

-

D94

PEG_TX[13]+ B70

HSOp(13) -

-

-

-

-

-

47